# LOW POWER DIGITAL FILTER IMPLEMENTATION IN FPGA FOR HEARING AID APPLICATION

Jitendra Kumar Das

**Department of Electronics & Communication Engineering National Institute of Technology Rourkela**

## LOW POWER DIGITAL FILTER IMPLEMENTATION IN FPGA FOR HEARING AID APPLICATION

A thesis submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy in Electronics & Communication Engineering

Ву

Jitendra Kumar Das Roll No: 50609001

Under the supervision of

Dr. Kamala Kanta Mahapatra Professor

Department of Electronics & Communication Engineering Pational Institute of Technology Rourkela

July, 2009

Dedicated

to

..... my Parents .....

Department of Electronics & Communication Engineering NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA ORISSA, INDIA - 769 008

CERTIFICATE

This is to certify that the thesis titled "Low Power Digital Filter Implementa-

tion in FPGA for Hearing Aid Application", submitted to the National

Institute of Technology, Rourkela by Jitendra Kumar Das, Roll No. 50609001

for the award of the degree of Doctor of Philosophy in Electronics & Com-

munication Engineering, is a bona fide record of research work carried out by

him under my supervision and guidance.

The candidate has fulfilled all the prescribed requirements.

The thesis, which is based on candidate's own work, has not been submitted

elsewhere for the award of a degree.

In my opinion, the thesis is of the standard required for the award of Doctor

of Philosophy in Electronics & Communication Engineering.

To the best of my knowledge, he bears a good moral character and decent be-

haviour.

Prof. K. K. Mahapatra

**Professor**

Department of Electronics & Communication Engineering NATIONAL INSTITUTE OF TECHNOLOGY

Rourkela-769 008 (INDIA)

Email: kkm@nitrkl.ac.in

ii

#### ACKNOWLEDGEMENT

I would like to take this opportunity to extend my deepest gratitude to my teacher and supervisor, Prof. K. K. Mahapatra, for his continuous encouragement and active guidance. I am indebted to him for the valuable time he has spared for me during this work. He is always there to meet and talk about my ideas, to proofread and mark up my research papers and chapters, and to ask me good questions to help me think through my problems.

I am very much thankful to Prof. S. K. Patra, HOD, ECE Department for his continuous encouragement. Also, I am indebted to him who provided me all official and laboratory facilities.

I am grateful to Dr. S. Meher and Prof. T.K. Dan for his valuable suggestions and comments during this research period.

My sincere thanks go to Prof. G.S. Rath, Prof. S. K. Jena, Prof. A. K. Panda and Prof. B.D. Sahoo whose valuable suggestions helped me a lot in completing this thesis.

In addition, let me thank all my friends Saroj, Pankaj, Sushant, Manas, Debi Mohanty, Nilamani Bhoi, Sudeendra Kumar, Ayas Kanta and Peter for their great support and encouragement during the research period. Also, I am thankful to all the non-teaching staffs of ECE Department for their kind cooperation.

During the course of this work, I am supported by a project VLSI-SMDP sponsored by DIT, Govt. of India. I am really thankful to them.

Last but not the least, I take this opportunity to express my regards and obligation to my father-in-laws and family members for encouraging me in all expects. I would also like to thankful my wife *Dugulu* and son *Omm* for their unconditional support and encouragement in carrying my Ph. D work.

Jitendra Kumar Das

## BIO-DATA OF THE CANDIDATE

Name of the Candidate : Jitendra Kumar Das

Father's Name : Gopinath Das

AT/PO- Nuapatna(T)

Permanent Address : PS- Tigiria, Cuttack

Orissa 754035

Email ID : jkdas12@gmail.com

#### **ACADEMIC QUALIFICATION**

• Continuing **Ph. D.** in Electronics & Communication Engineering, National Institute of Technology Rourkela, Orissa (INDIA). Year of degree awarded or expected -2009-10.

- M. Tech. in Electrical Engineering (Electronics System and Communication), National Institute of Technology Rourkela, Orissa (INDIA).

- **B. E.** (Electronics and Telecommunication), Utkal University, Orissa, (INDIA).

#### **PUBLICATION**

Published/ 04 papers in National and International Conferences which are listed in page 164 as "Contribution by the candidate".

#### **Abstract**

Digital filters suitable for hearing aid application on low power perspective have been developed and implemented in FPGA in this dissertation.

Hearing aids are primarily meant for improving hearing and speech comprehensions. Digital hearing aids score over their analog counterparts. This happens as digital hearing aids provide flexible gain besides facilitating feedback reduction and noise elimination. Recent advances in DSP and Microelectronics have led to the development of superior digital hearing aids. Many researchers have investigated several algorithms suitable for hearing aid application that demands low noise, feedback cancellation, echo cancellation, etc., however the toughest challenge is the implementation. Furthermore, the additional constraints are power and area. The device must consume as minimum power as possible to support extended battery life and should be as small as possible for increased portability. In this thesis we have made an attempt to investigate possible digital filter algorithms those are hardware configurable on low power view point.

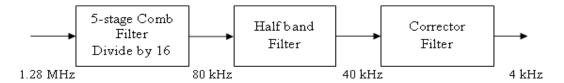

Suitability of decimation filter for hearing aid application is investigated. In this dissertation decimation filter is implemented using 'Distributed Arithmetic' approach. While designing this filter, it is observed that, comb-half band FIR-FIR filter design uses less hardware compared to the comb-FIR-FIR filter design. The power consumption is also less in case of comb-half band FIR-FIR filter design compared to the comb-FIR-FIR filter. This filter is implemented in Virtex-II pro board from Xilinx and the resource estimator from the system generator is used to estimate the resources.

However 'Distributed Arithmetic' is highly serial in nature and its latency is high; power consumption found is not very low in this type of filter implementation. So we have proceeded for 'Adaptive Hearing Aid' using Booth-Wallace tree multiplier. This algorithm is also implemented in FPGA and power calculation of the whole system is done using Xilinx Xpower analyser. It is observed that power consumed by the hearing aid with Booth-Wallace tree multiplier is less than the hearing aid using Booth multiplier (about 25%). So we can conclude that the hearing aid using Booth-Wallace tree multiplier consumes less power comparatively.

The above two approached are purely algorithmic approach. Next we proceed to combine circuit level VLSI design and with algorithmic approach for further possi-

ble reduction in power.

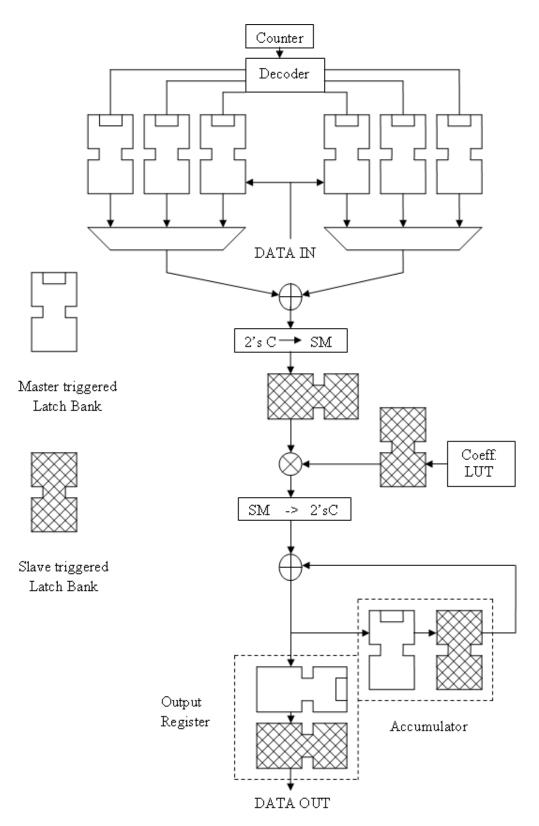

A MAC based FDF-FIR filter (algorithm) that uses dual edge triggered latch (DET) (circuit) is used for hearing aid device. It is observed that DET based MAC FIR filter consumes less power than the traditional (single edge triggered, SET) one (about 41%). The proposed low power latch provides a power saving upto 65% in the FIR filter. This technique consumes less power compared to previous approaches that uses low power technique only at algorithmic abstraction level.

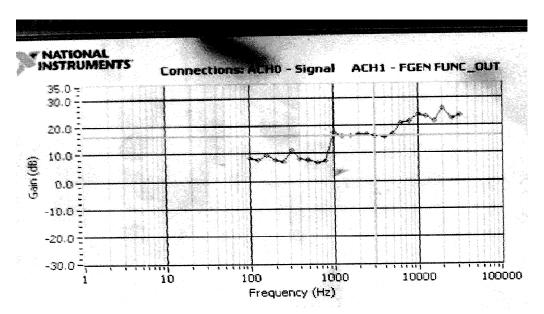

The DET based MAC FIR filter is tested for real-time validation and it is observed that it works perfectly for various signals (speech, music, voice with music). The gain of the filter is tested and is found to be 27 dB (maximum) that matches with most of the hearing aid (manufacturer's) specifications. Hence it can be concluded that FDF FIR digital filter in conjunction with low power latch is a strong candidate for hearing aid application.

#### **List of Abbreviations**

**ADC** Analog to Digital convertor

**ASIC** Application Specific Integrated Circuits

CIC Completely- in Canal

**CLA** Carry Look Ahead Adder CPACarry Propagate adder

**CSA** Carry Save Adder

Carry Save Adder Tree **CSAT**

DAC Digital to Analog Converter

**DET** Dual-edge Triggered

**DETSE** Dual-edge Triggered Storage Elements

**DSP** Digital Signal Processing

Folded Direct Form **FDF**

FFFlip-flop **FFs** Flip-flops

FIR Finite Impulse Response

**GPP** General Purpose processor

*IO* Input Output

**LMS** Least Mean Square LSB Least Significant Bit

Look up Table **LUT**

**MAC** Multiply and accumulate **MSB** Most Significant Bit

MSI

**MUX** Multiplexer

**PCM** Pulse Code Modulation RLS Recursive Least Square RTLRegister Transfer Level **SET** Single-edge Triggered

**SETSE** Single Edge Triggered Storage Elements

Medium Scale Integration

**VHDL** Very High Speed Integrated Circuit Description Language

**VLSI** Very Large Scale Integration

## **List of Figures**

| Figure No.   | <u>Name</u>                                                     | Page no. |

|--------------|-----------------------------------------------------------------|----------|

| Figure 1.1:  | Analog Signal Processing                                        | 6        |

| Figure 1.2:  | Block Diagram of a Digital Signal Processing System             | 6        |

| Figure 1.3:  | Generic DSP Processor Architecture                              | 10       |

| Figure 1.4:  | Basic Idea of a Filter                                          | 11       |

| Figure 1.5:  | Basic Set-Up of a Digital Filter                                | 12       |

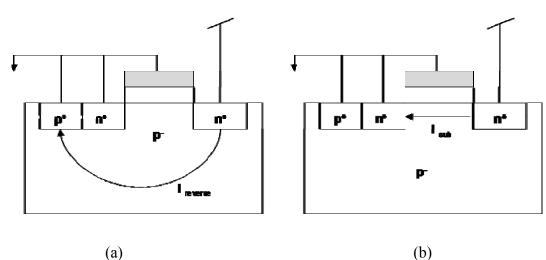

| Figure 2.1:  | Leakage current types                                           | 27       |

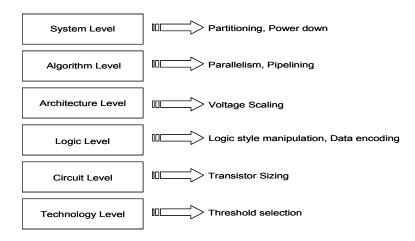

| Figure 2.2:  | Low-power design methodology at different abstraction levels.   | 29       |

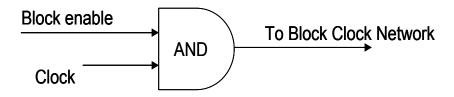

| Figure 2.3:  | Clock gating.                                                   | 30       |

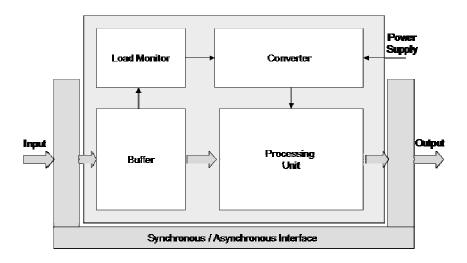

| Figure 2.4:  | Asynchronous design with dynamic voltage scaling.               | 30       |

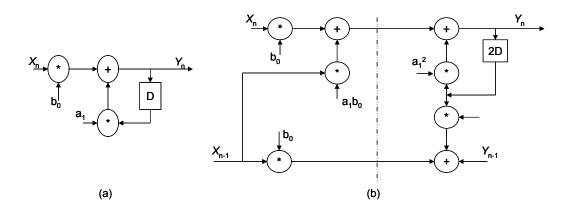

| Figure 2.5:  | (a) Original signal flow graph. (b) Unrolled signal flow graph. | 31       |

| Figure 2.6:  | Original data path.                                             | 32       |

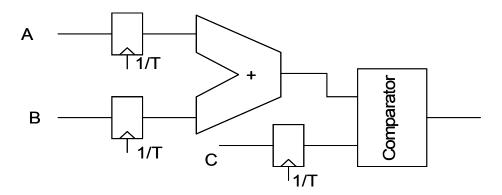

| Figure 2.7:  | Parallel implementation.                                        | 33       |

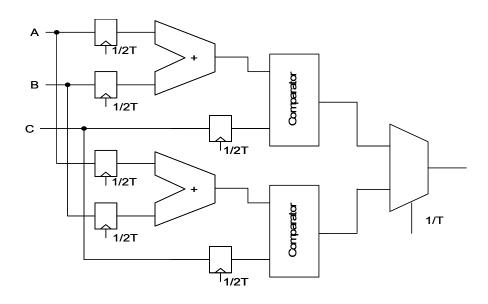

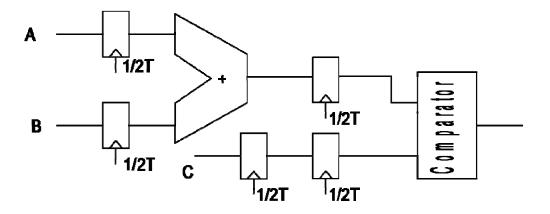

| Figure 2.8:  | Pipelined implementation                                        | 33       |

| Figure 2.9:  | A pre-computation structure for low power.                      | 34       |

| Figure 2.10: | A two input NAND gate.                                          | 37       |

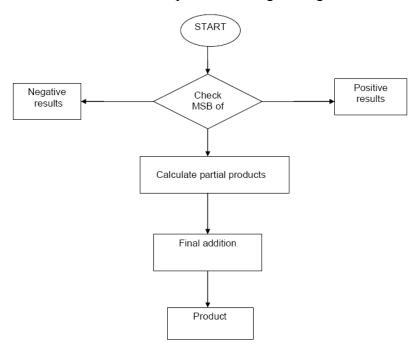

| Figure 2.11: | Basic binary multiplication                                     | 40       |

| Figure 2.12: | Signed multiplication algorithm                                 | 40       |

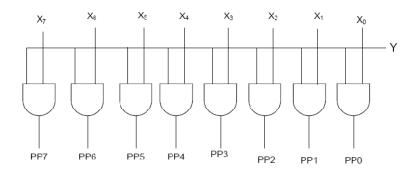

| Figure 2.13: | Partial product generation logic                                | 41       |

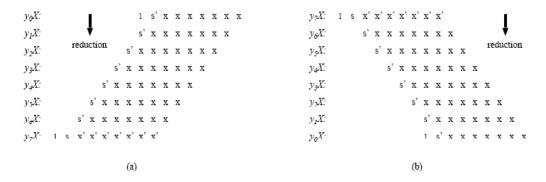

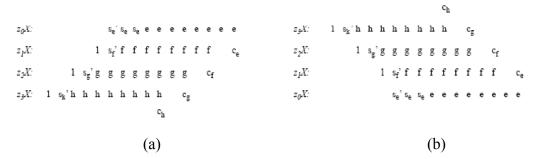

| Figure 2.14: | Radix-2 PP bit matrix(n=8): (a) RL; (b) LR                      | 42       |

| Figure 2.15: | Radix-4 PP bit matrix(n=8) : (a) RL;(b) LR                      | 42       |

| Figure 2.16: | A radix-2 8X8 RL multiplier                                     | 43       |

| Figure 2.17: | Radix-2 LR carry save array multiplier (n=8)                    | 43       |

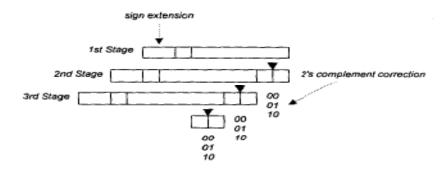

| Figure 2.18: | Radix-2 LR carry save array multiplier (n=12)                   | 44       |

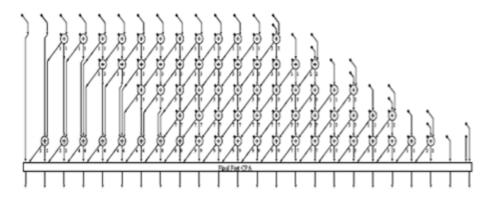

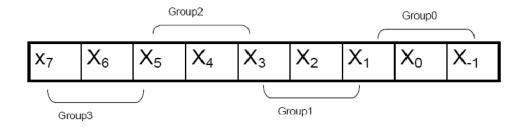

| Figure 2.19: | Multiplier bit grouping according to Booth Encoding             | 45       |

| Figure 2.20: | Add and shift method of partial product generation              | 47       |

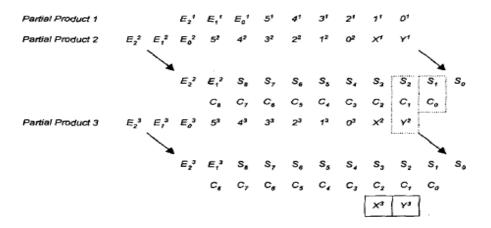

| Figure 2.21: | Partial product generation for 6x6 bit modified Booth           |          |

|              | Multiplication                                                  | 50       |

| Figure 2.22: | Data flow of a 6X6 bit modified Booth multiplication            |          |

|              | with the partial                                                | 50       |

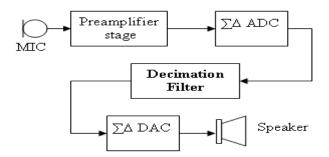

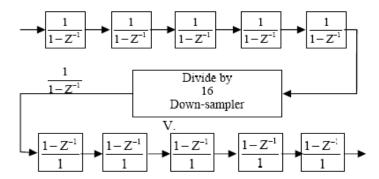

| Figure 3.1:  | The Decimation filter used for the hearing aid application      | 52       |

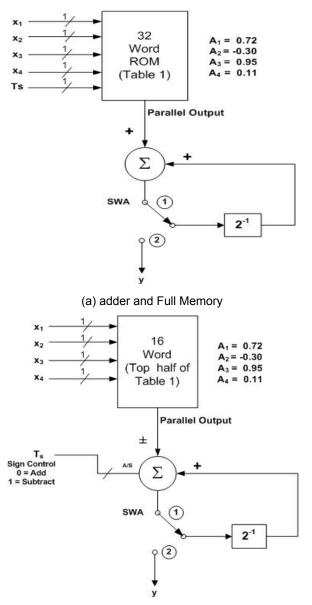

| Figure 3.2:  | Structure of ROM for K=4                                        | 55       |

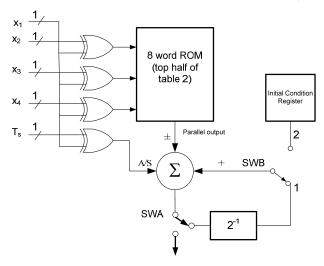

| Figure 3.3:  | AD Converter Block Diagram                                      | 60       |

| Figure 3.4:  | Requirements of anti-aliasing filter                            | 61       |

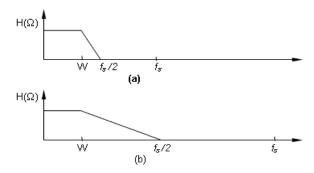

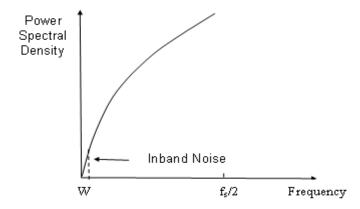

| Figure 3.5:  | Power Spectral Density for FIRST Order Sigma-Delta coder        | 62       |

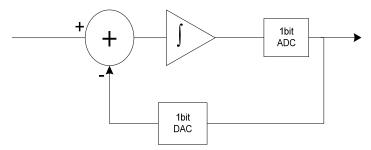

| Figure 3.6:  | Oversampled Delta modulator                                     | 63       |

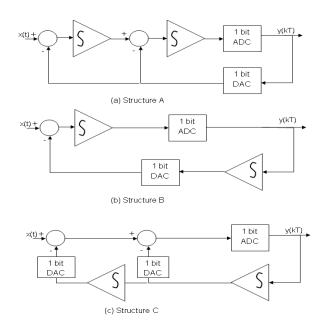

| Figure 3.7:  | Three different structures of $\sum \Delta$ modulators          | 64       |

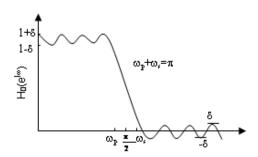

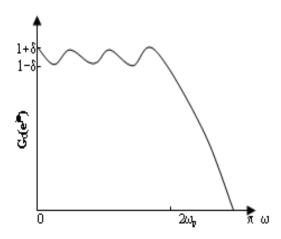

| Figure 3.8:  | Amplitude response of a half-band FIR filter                    | 66       |

| Figure 3.9:  | Amplitude response                                              | 68       |

| Figure 3.10: | Normalized Frequency                                            | 68       |

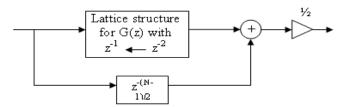

| Figure 3.11: | Structure of half-band filter                                   | 69       |

| Figure 3.12: | Basic process of sampling rate conversion                       | 70       |

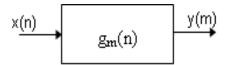

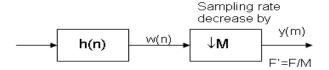

| Figure 3.13: | Sampling rate reduction by factor M                             | 72       |

| Figure 3.14: | Block diagram typical spectra for sampling rate reduction by    |          |

|              | factor M                                                        | 72       |

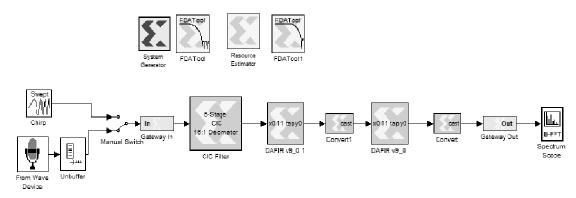

| Figure 3.15: | Simulink block diagram of the decimation filter implemented     | 74       |

| Figure 3.16: | Decimation filter                                               | 76       |

| Figure 3.17: | Comb filter with decimation factor 16                           | 76       |

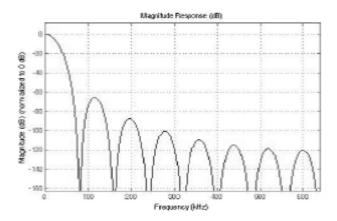

| Figure 3.18: | Response of 5 stage comb filter                                 | 77       |

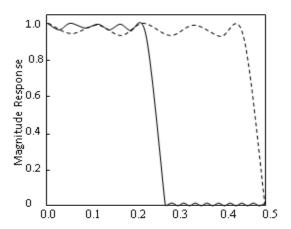

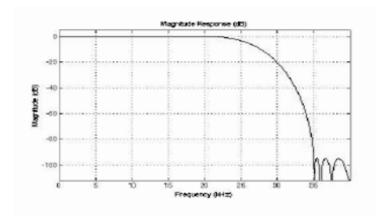

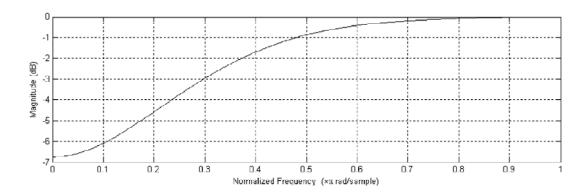

| Figure 3.19: | Magnitude response of half band filter                          | 78       |

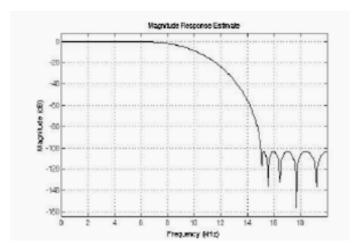

| Figure 3.20: | Magnitude response of last stage corrector filter               | 78       |

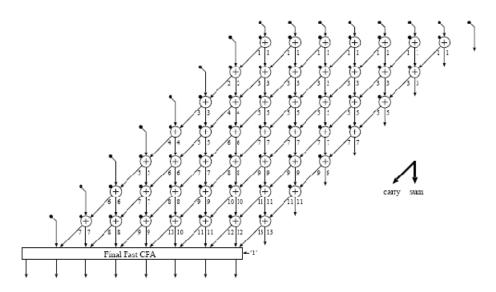

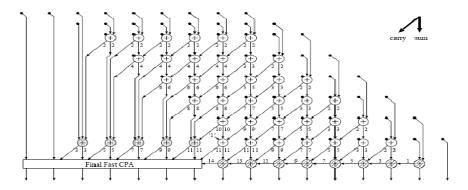

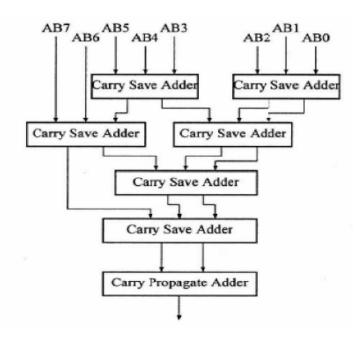

| Figure 4.1:  | Wallace tree multiplier                                         | 82       |

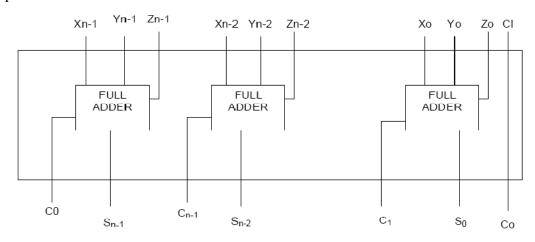

| Figure 4.2:  | Implementation of n bit CSA operation                               | 83  |

|--------------|---------------------------------------------------------------------|-----|

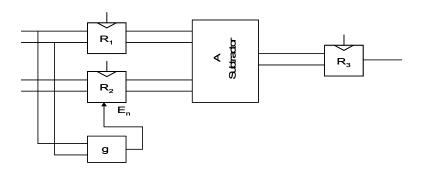

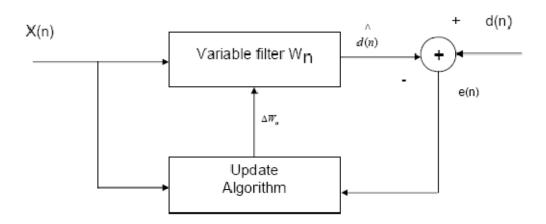

| Figure 4.3:  | Block diagram of an adaptive filter                                 | 86  |

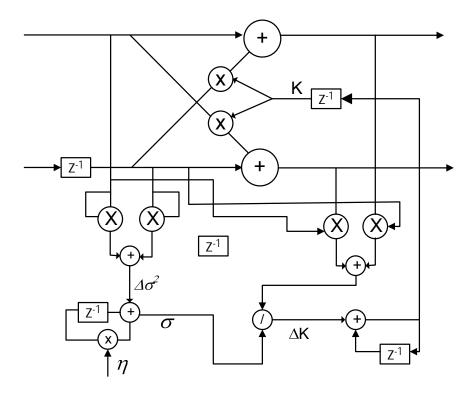

| Figure 4.4:  | Adaptive gradient lattice filter                                    | 88  |

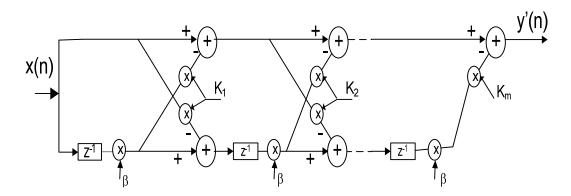

| Figure 4.5:  | Analysis filter $(1-A(z/\beta), x(n))$ is input and y'(n) is output | 89  |

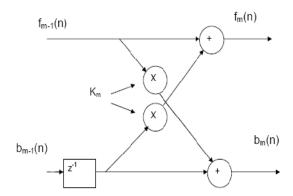

| Figure 4.6:  | Single stage of analysis filter                                     | 90  |

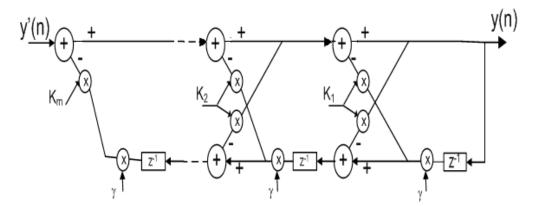

| Figure 4.7:  | Synthesis filter, y'(n) input and y(n) is output                    | 92  |

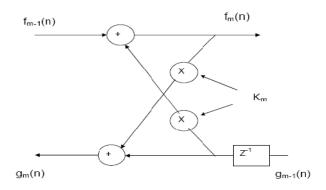

| Figure 4.8:  | Single stage of sysnthesi filter                                    | 93  |

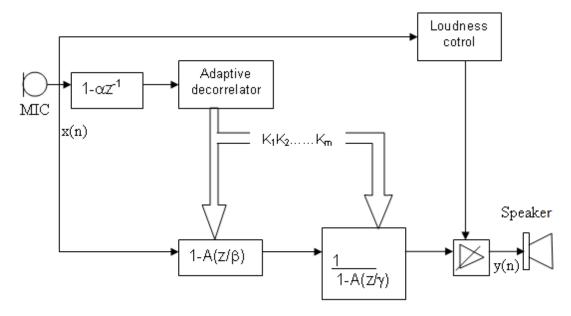

| Figure 4.9:  | Block diagram of Spectral Sharpening for Speech                     |     |

| C            | Enhancement.                                                        | 94  |

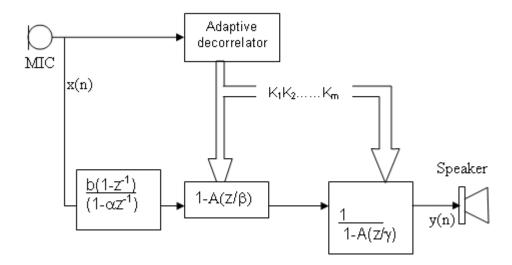

| Figure 4.10: | Block diagram of Spectral Sharpening by Noise Reduction             | 96  |

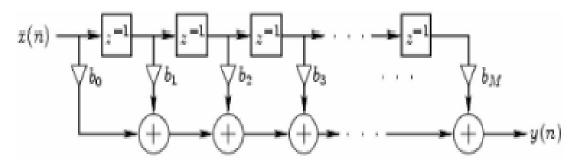

| Figure 4.11: | General causal FIR filter structure                                 | 97  |

| Figure 4.12: | Magnitude response of an high pass FIR filter                       | 99  |

|              | (cut off frequency 700HZ)                                           |     |

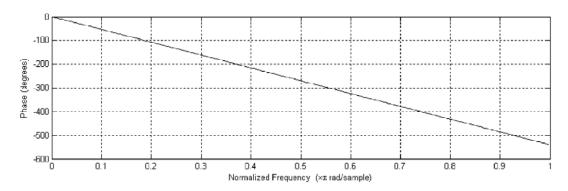

| Figure 4.13: | Phase response of a high pass FIR filter                            | 99  |

|              | (cut off frequency 700HZ).                                          |     |

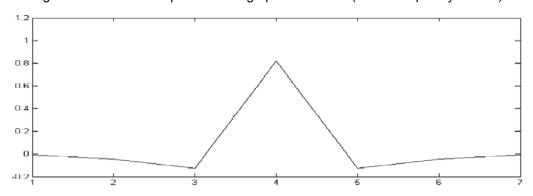

| Figure 4.14: | Impulse response of a high pass FIR filter                          | 99  |

|              | (cut off frequency 700HZ)                                           |     |

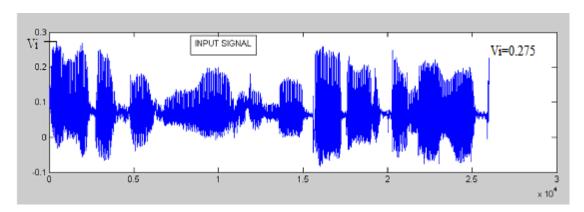

| Figure 4.15: | Waveform of the 2.6 second speech input                             | 100 |

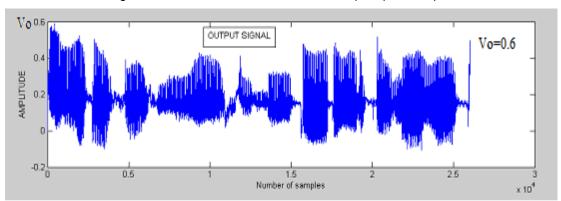

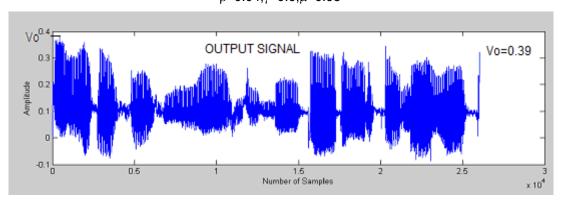

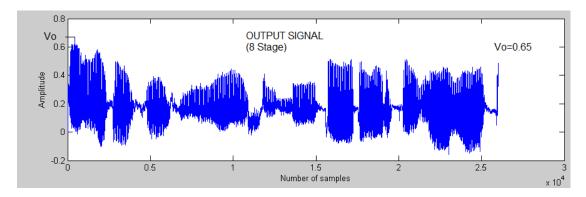

| Figure 4.16: | Waveform of the 2.6 second hearing aid output using                 |     |

|              | Parameters $\beta = 0.3, \gamma = 0.7, \mu = 0.98$ .                | 100 |

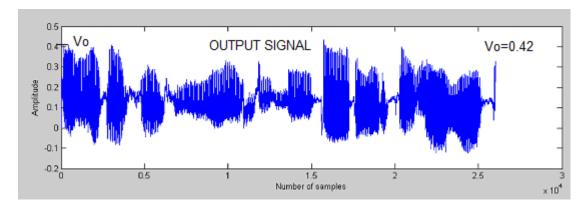

| Figure 4.17: | Waveform of the 2.6 second hearing aid output using                 |     |

|              | parameters $\beta = 0.3, \gamma = 0.7, \mu = 0.98$ .                | 100 |

| Figure 4.18: | Waveform of the 2.6 second hearing aid output using                 |     |

| C            | Parameters $\beta = 0.4, \gamma = 0.6, \mu = 0.98$ .                | 101 |

| Figure 4.19: | Waveform of the 2.6 second hearing aid output using                 |     |

| J            | parameters $\beta = 0.4, \gamma = 0.6, \mu = 0.98$                  | 101 |

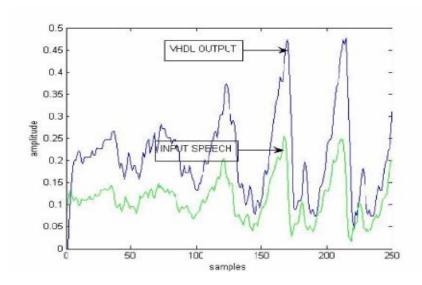

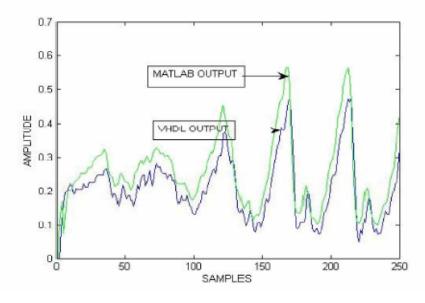

| Figure 4.20: | Comparision of input speech signal with output using                |     |

| J            | vhdl for 250 samples                                                | 103 |

| Figure 4.21: | Comparison of the MATLAB output speech signal with the              |     |

| C            | Matalab output                                                      | 103 |

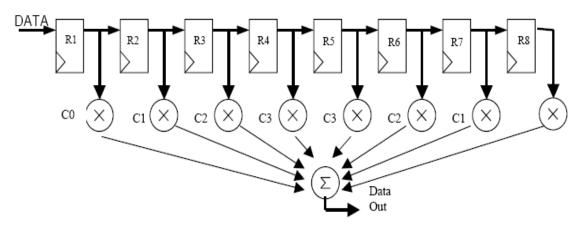

| Figure 5.1:  | Tap delay line filter or transversal FIR filter                     | 107 |

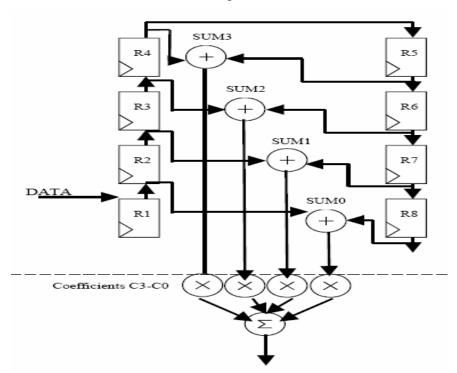

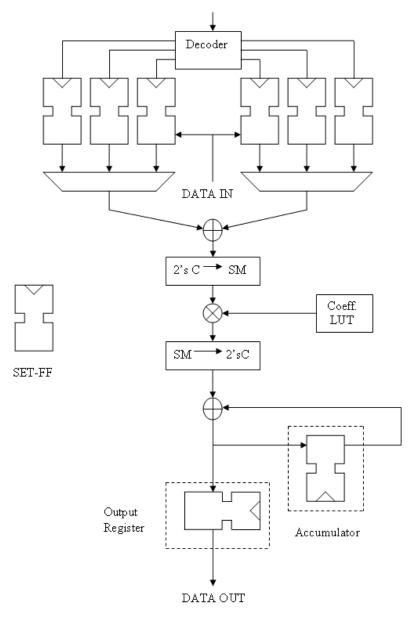

| Figure 5.2:  | Folded Direct form FIR Filter Architecture                          | 107 |

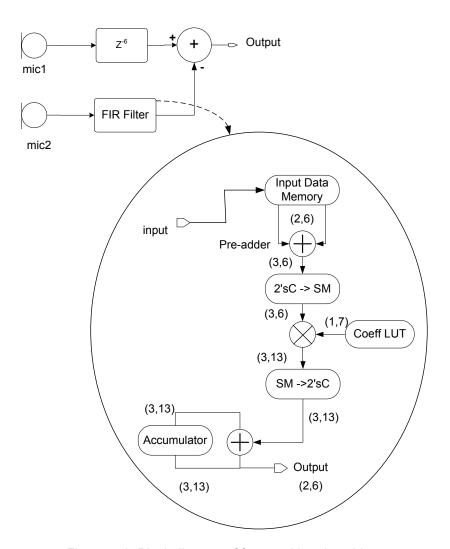

| Figure 5.3:  | Block diagram of front end hearing aid                              | 108 |

| Figure 5.4:  | System Clocking Waveforms and General                               |     |

| C            | Finite-State Machines                                               | 110 |

| Figure 5.5:  | Clock Parameters: Period, Width, Clock Skew and                     |     |

|              | Clock Jitter                                                        | 111 |

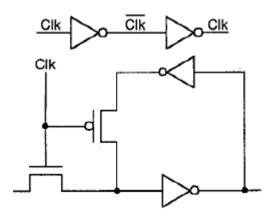

| Figure 5.6:  | Signal Relationship of an ideal Latch.                              | 112 |

| Figure 5.7:  | Signal Relationship of an Ideal Leading-Edge Triggered              |     |

|              | Flip-Flop                                                           | 113 |

| Figure 5.8:  | Single Edge Triggered Flip-Flop                                     | 113 |

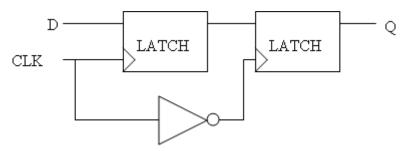

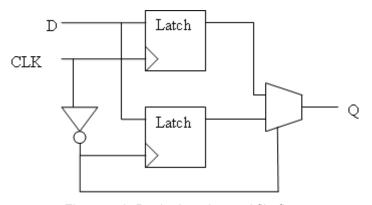

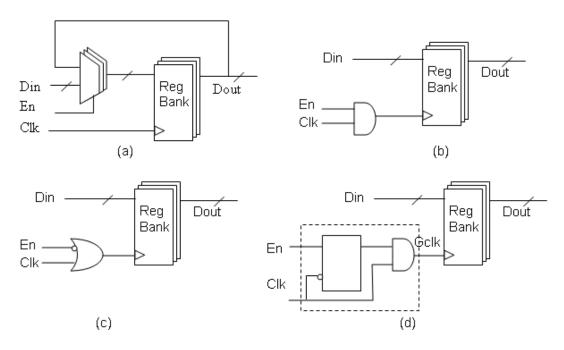

| Figure 5.9:  | Dual Edge Triggered Flip-Flop                                       | 113 |

| Figure 5.10: | clock gating at various levels                                      | 116 |

| Figure 5.11: | Traditional Clock Gating Applied to a Register File                 | 120 |

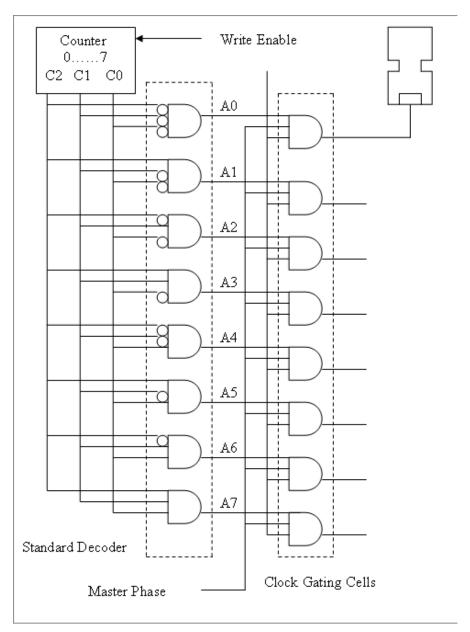

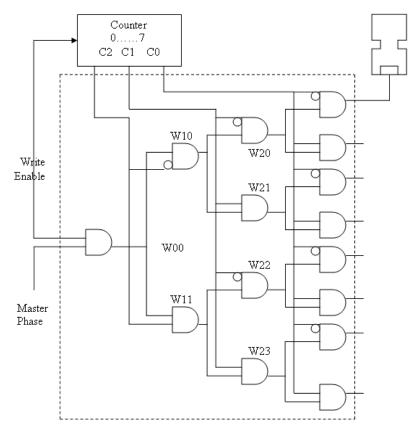

| Figure 5.12: | Multistage clock gating decoder                                     | 121 |

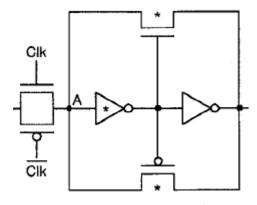

| Figure 5.13: | Block Diagram of Original Low Power D-Latch                         | 123 |

| Figure 5.14: | Block Diagram Low Power and Low Voltage D-Latch                     | 123 |

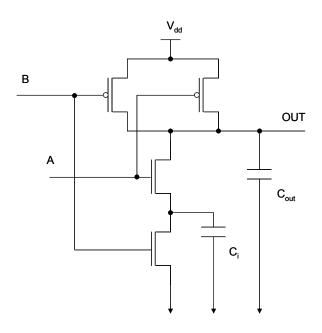

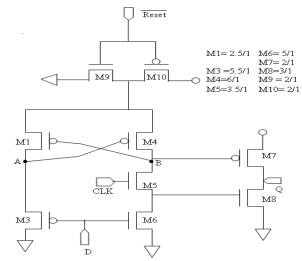

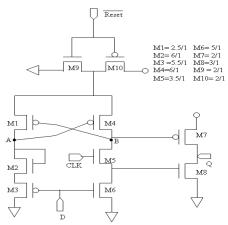

| Figure 5.15: | Low power latch circuits using 9 transistors                        | 125 |

| Figure 5.16: | Low power latch circuits using 10 transistors                       | 125 |

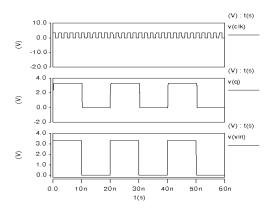

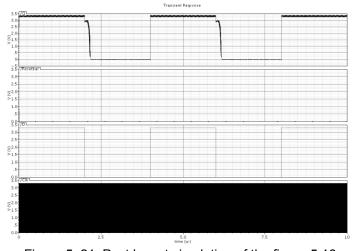

| Figure 5.17: | Result of dff with 350nm tech at 3.3V with power loss               | 120 |

| <i>G.</i>    | of 21µW at 250 MHz                                                  | 126 |

| Figure 5.18: | Result of dff with 350nm tech with reset logic tech 3.3V            | 120 |

| G 2 3.23.    | with power loss of 22µW at 250 MHz                                  | 126 |

|              | WILL DUWLI 1055 OI 44H W at 45U WILL.                               | 120 |

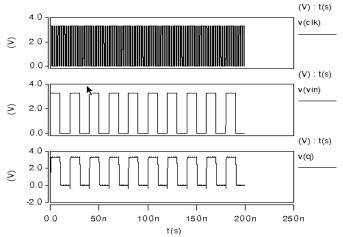

| Figure 5.19: | Simulation result of the circuit 5.16 with 180 nM technology. | 127 |

|--------------|---------------------------------------------------------------|-----|

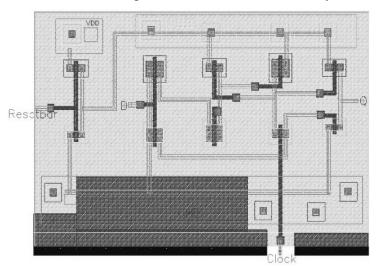

| Figure 5.20: | Proposed low power latch layout of with reset.                | 127 |

| Figure 5.21: | Post layout simulation of the figure 5.16                     | 127 |

| Figure 5.22: | Block diagram of FIR filter with traditional clocking         | 128 |

| Figure 5.23: | Block diagram of the FIR filter with dual edge clock gating   |     |

|              | Strategy                                                      | 129 |

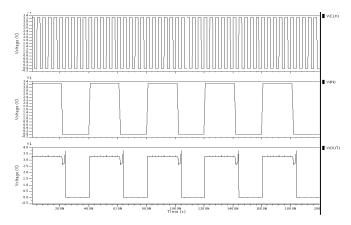

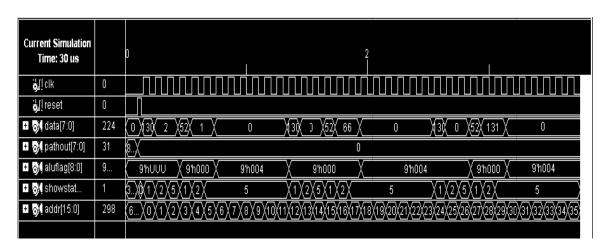

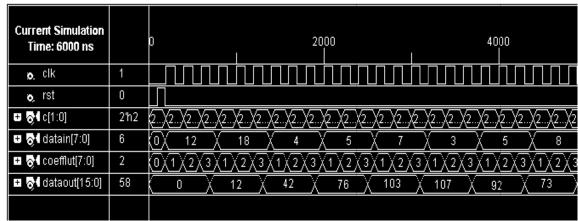

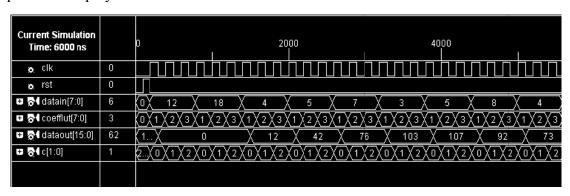

| Figure 5.24: | Simulation Output of a 6-Tap FIR Filter Program               | 130 |

| Figure 5.25: | Simulation Output of a 6-Tap FIR Filter Block Diagram         |     |

|              | Using Single Edge Triggered Clocking Strategy.                | 131 |

| Figure 5.26  | Simulation Output of a 6-Tap FIR Filter Block Diagram         |     |

|              | Using Proposed Clocking Strategy.                             | 131 |

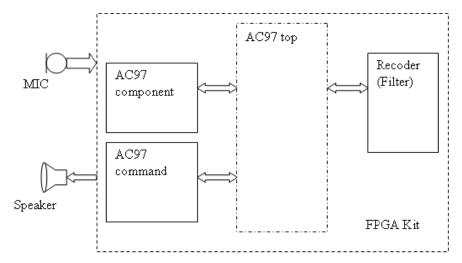

| Figure 6.1:  | Functional block diagram of the hardware setup                | 135 |

| Figure 6.2:  | Hardware validation setup for filter implementation in        |     |

|              | virtex-II pro board.                                          | 135 |

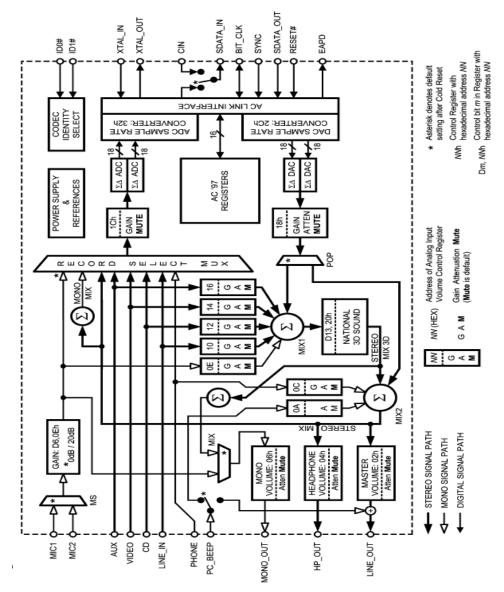

| Figure 6.3:  | Functional diagram of the AC'97 codec                         | 136 |

| Figure 6.4:  | Register content for accessing different sections of a        |     |

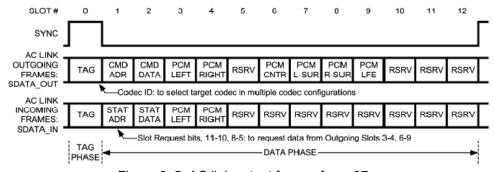

|              | AC'97 codec                                                   | 138 |

| Figure 6.5:  | AC link Output Frames for AC'97                               | 138 |

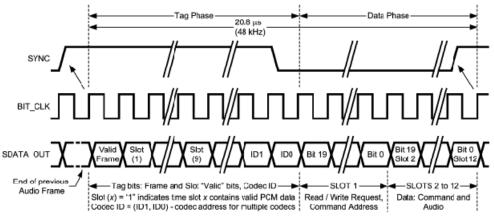

| Figure 6.6:  | Structure of Output frame                                     | 139 |

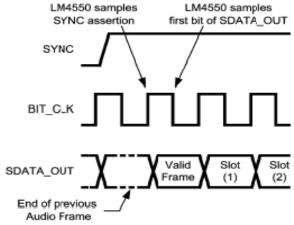

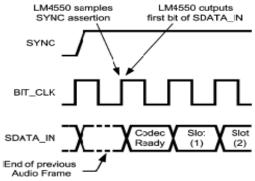

| Figure 6.7:  | Start of a Output frame                                       | 139 |

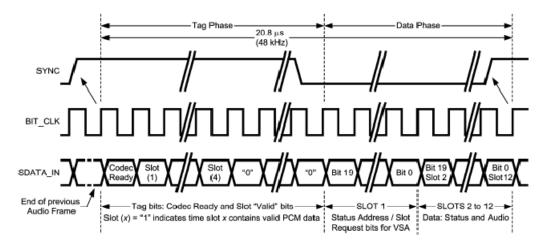

| Figure 6.8:  | AC link input frame                                           | 141 |

| Figure 6.9:  | Start of input frame                                          | 141 |

| Figure 6.10: | FIR filter structure with dual edge triggering for hardware   |     |

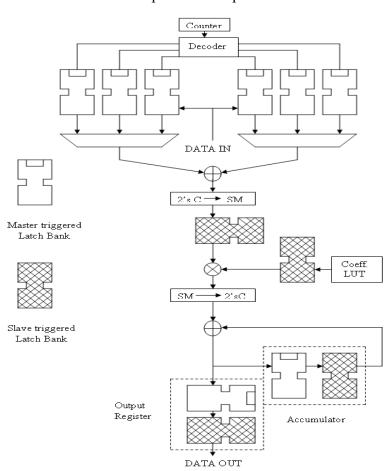

|              | Implementation                                                | 143 |

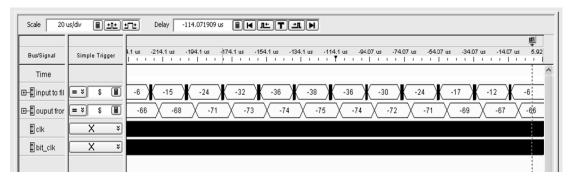

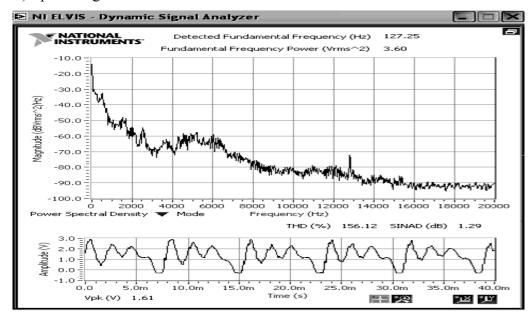

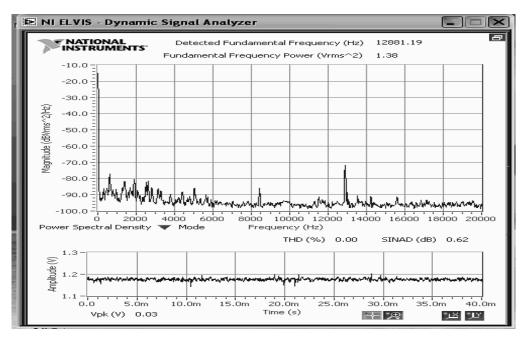

| Figure 6.11: | Spectrum analyser output of input and output data             | 144 |

| Figure 6.12: | Spectrum of speech signal without filter implementation       | 144 |

| Figure 6.13: | Amplitude spectrum of the speech signal after filtering       | 145 |

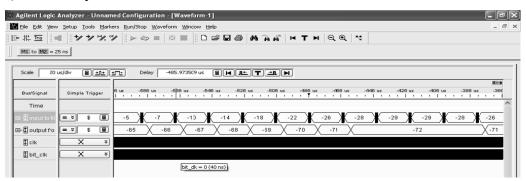

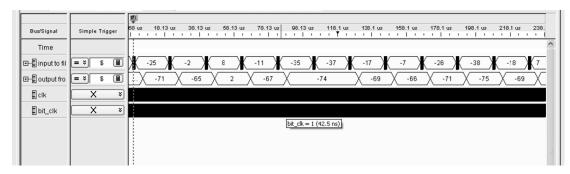

| Figure 6.14: | Logic analyser output of the filter for music signal only     | 145 |

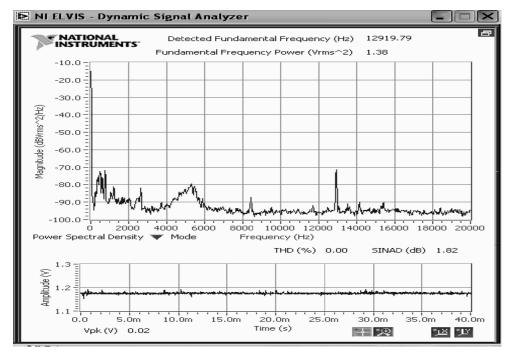

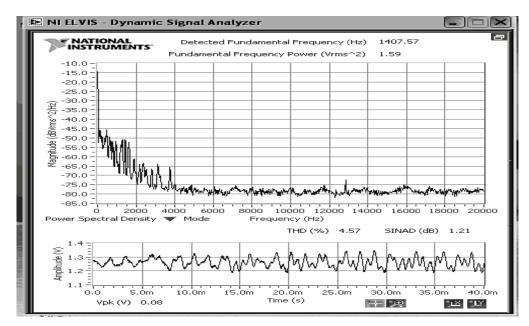

| Figure 6.15: | Amplitude spectrum of the music signal taken                  | 146 |

| Figure 6.16: | Amplitude spectrum of the music signal after filtering        | 146 |

| Figure 6.17: | Output of the logic analyser after filtering the signal       | 147 |

|              | (music and voice).                                            |     |

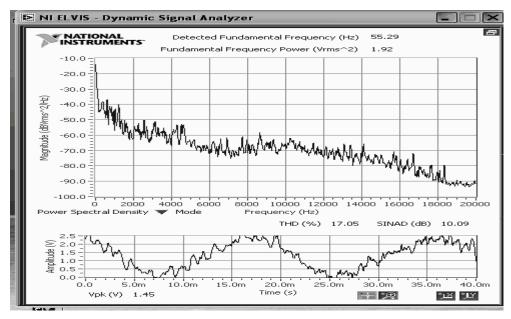

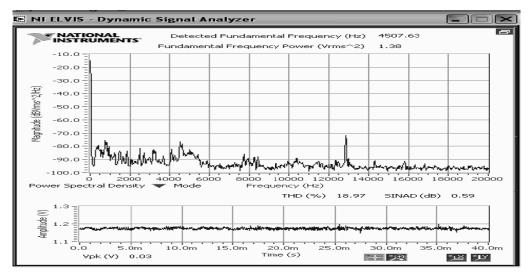

| Figure 6.18: | Amplitude spectrum of a signal containing music and voice     | 147 |

| Figure 6.19: | Amplitude spectrum of the signal after filtering the signal   | 147 |

|              | (music and voice).                                            |     |

| Figure 6.20: | Gain plot of the amplifier                                    | 148 |

| Con  | Contents                                                 |           |

|------|----------------------------------------------------------|-----------|

|      | ificate                                                  | ii<br>iii |

|      | Acknowledgement Bio-data of Candidate                    |           |

| Abst |                                                          | ıv<br>vi  |

| List | of Abbreviations                                         | vii       |

| List | of figures                                               | viii      |

| Cha  | pter – I                                                 |           |

|      | oduction                                                 |           |

| 1.1  | Hearing Aids                                             | 2         |

| 1.2  | Motivation                                               | 3         |

| 1.3  | Signal Processing                                        | 4         |

| 1.4  | DSP Processor                                            | 7         |

| 1.5  | Digital Filters                                          | 11        |

| 1.6  | Algorithms for Hearing Aid Design                        | 13        |

| 1.7  | Objective of the thesis                                  | 17        |

| 1.8  | Organisation of thesis                                   | 18        |

| Cha  | pter - II                                                |           |

|      | Power VLSI Techniques for Digital Filters for Hearing    | g aid     |

| app  | lications                                                |           |

| 2.1  | Review of Low Power Methods used in Filters              | 21        |

| 2.2  | Basics of Low power VLSI Design                          | 25        |

| 2.3  | Power Dissipation Sources                                | 26        |

| 2.4  | Low Power Techniques                                     | 29        |

| 2.5  | Multiplier structure review                              | 38        |

| Cha  | pter - III                                               |           |

|      | imation Filter for Hearing Aid Application using Distrib | outed     |

|      | hmetic                                                   |           |

| 3.1  | Introduction                                             | 52        |

| 3.2  | Distributed Arithmetic                                   | 52        |

| 3.3  | Oversampling Technique for Analog to Digital Conversion  | 59        |

| 3.4  | Half-band filter                                         | 65        |

| 3.5  | Decimation                                               | 69        |

| 3.6  | Hearing Aid Implementation                               | 74        |

| 3.7  | Results & Conclusion                                     | 78        |

## Chapter - IV

|                               | Adaptive Hearing Aid Algorithm using Booth-Wallace Tree tiplier                       |         |

|-------------------------------|---------------------------------------------------------------------------------------|---------|

| 4.1                           | Introduction                                                                          | 81      |

| 4.2                           | Wallace Tree Multiplier                                                               | 81      |

| 4.3                           | Adaptive lattice filter                                                               | 86      |

| 4.4                           | Hearing Aid Design                                                                    | 93      |

| 4.5                           | Experimental results and conclusion                                                   | 99      |

| Cha                           | pter - V                                                                              |         |

|                               | Power Filter Design using a Novel Dual Edge Triggered La                              | tch     |

| 5.1                           | Introduction                                                                          | 106     |

| 5.2                           | FIR Filters                                                                           | 106     |

| 5.3                           | Hearing Aid structure                                                                 | 108     |

| 5.4                           | Clocking Strategy                                                                     | 109     |

| 5.5                           | Low Power Latch                                                                       | 123     |

| 5.6                           | MAC based FIR Filter Structures and Simulation and Conclusion                         | 128     |

| Cha                           | pter - VI                                                                             |         |

|                               | l Time Experimental Set Up and Results for FIR Filter using<br>I Edge Triggered Latch | g Novel |

| 6.1                           | Introduction                                                                          | 134     |

| 6.2                           | Functional description of the AC'97 codec                                             | 136     |

| 6.3                           | Output Frame from AC97                                                                | 137     |

| 6.4                           | AC Link Input Frame                                                                   | 140     |

| 6.5                           | Structure of the filter implemented                                                   | 142     |

| 6.6                           | Results and conclusion                                                                | 144     |

| 6.7                           | Conclusion                                                                            | 148     |

| Cha                           | pter - VII                                                                            |         |

| Con                           | clusion                                                                               |         |

| 7.1                           | Introduction                                                                          | 150     |

| 7.2                           | Conclusions                                                                           | 150     |

| 7.3                           | Scope for future work                                                                 | 152     |

| Refe                          | rences                                                                                | 153     |

| Contribution by the candidate |                                                                                       | 164     |

# Chapter - I Introduction

#### 1.1 Hearing Aids

A hearing aid is a small electronic device that one wears in or behind his/her ear. It makes sounds louder so that a person with hearing loss can listen, communicate, and participate better in daily activities. A hearing aid can help people hear more in both quiet and noisy situations. A hearing aid has three basic parts: a microphone, amplifier, and speaker. The hearing aid receives sound through a microphone, which converts the sound waves to electrical signals and sends those to an amplifier. The amplifier increases the power of the signals and then sends to the ear through a speaker.

Hearing aids are primarily useful in improving the hearing and speech comprehension of people who have hearing loss that results from damage to the small sensory cells in the inner ear, called hair cells. The damage can occur as a result of disease, aging, or injury from noise or certain medicines.

A hearing aid magnifies sound vibrations entering the ear. Surviving hair cells detect the larger vibrations and convert them into neural signals that are passed along to the brain. The greater the damage to a person's hair cells, the more severe is the hearing loss, and the greater the hearing aid amplification needed to be larger. However, there are practical limits to the amount of amplification a hearing aid can provide. In addition, if the inner ear is too damaged, even large vibrations will not be converted into neural signals. In this situation, a hearing aid would be ineffective [1].

There are three basic styles of hearing aids. The styles differ by size, their placement on or inside the ear, these are

- **Behind-the-ear** (BTE) hearing aids consist of a hard plastic case worn behind the ear and connected to a plastic earmold that fits inside the outer ear.

- **In-the-ear** (ITE) hearing aids fit completely inside the outer ear and are used for mild to severe hearing loss.

- Canal aids fit into the ear canal and are available in two styles. The inthe-canal (ITC) hearing aid is made to fit the size and shape of a person's ear canal. A completely-in-canal (CIC) hearing aid is nearly hidden in the ear canal. Both types are used for mild to moderately severe hearing loss.

Awareness on hearing aids and its design [2] has made an important topic of research. Acoustic noise, acoustic feedback problems in the hearing aids have become more noticeable. In daily life undesirable effect of noise, acoustic feedback in hearing aid is very annoying. The use of modern technology, light weight, low power device has made an impact in the development of hearing aids. In this dissertation we have made an attempt to design a class of low power digital filter suitable for hearing aid application.

#### 1.2 Motivation

Approximately 10% of the population suffers from some hearing loss, however only a small percentage of these categories actually use a hearing aid device. There are several factors affecting market penetration like

- a. Stigma associated with wearing the device.

- b. Customer dissatisfaction with the devices not meeting their performances.

- c. Cost associated with devices.

Rapid advancements in DSP and Microelectronics have facilitated the growth and use of hearing aids and its related research. DSP techniques have certain advantages like

- a. Less sensitive to component parameters and environmental parameters.

- b. It allows changing the processor characteristics during processing such as implementation of adaptive filters.

- c. DSP can be applied to low frequency signals (Hearing Aid operates physically from 300 Hz to 4 kHz).

With these advantages, DSP provides an efficient way for managing signal processing in our daily life. Recent development of commercial hearing aid devices and DSP technique has allowed the developer to accommodate advanced signal processing techniques in hearing aid devices. This results in accurate reproduction of the sound with minimum distortion. Almost all major hearing aid manufacturers have digital hearing aid products in the markets, but only 20% of those devices are acquired by different users. This is due to large size and high power consumption. To mitigate the above

mentioned problems, it is required to find suitable low power algorithms that should additionally meet area constraints in VLSI design.

Hence the most serious issue of hearing aid device is that it should consume low power. To investigate this issue, we have investigated three different types of filter in designing low power filters. All filter designs are investigated and a structure has been proposed for low power implementation. Since hardware realization is important, all the structures in this thesis have been implemented in FPGA for testing its operation and power estimation is being carried out in each case. To bring out further insight real-time signal are applied to one of the structure for further validation. Therefore, basically we need to investigate

- a. Algorithm

- b. Low power VLSI.

#### 1.3 Signal Processing

Signal processing is the analysis, interpretation, and manipulation of signals. Signals are electrical representations of time-varying or spatial-varying physical quantities, either analog or digital, and may come from various sources. Signals of interest include speech, sound, images, radar signals, and many others. Processing of such signals includes filtering, storage and reconstruction, separation of information from noise (for example, aircraft identification by radar), compression (for example, image compression), and feature extraction (for example, speech-to-text conversion). Following are the two subfields of signal processing [3].

- a. Analog Signal Processing

- b. Digital Signal Processing

Digital signal processing is an area of science and engineering that has developed rapidly due to the significant advances in digital computer technology and integrated circuit fabrication. The rapid developments in integrated-circuit technology, starting from MSI to VLSI of electronic circuit has spurred the development of powerful, smaller, faster, and cheaper digital computers and special-purpose digital hardware. These inexpensive and relatively fast digital circuits have made it possible to construct highly sophisticated digital systems capable of performing complex digital signal processing functions and tasks, which are usually too difficult and/or too

expensive to be performed by analog circuitry or analog signal processing systems. Hence many of the signal processing tasks that were conventionally performed by analog means are realized today by less expensive and often more reliable digital hardware.

Not only do digital circuits yield cheaper and more reliable systems for signal processing they have other advantages as well. In particular, digital processing hardware allows programmable operations. Through software, one can more easily modify the signal processing functions to be performed by the hardware without modifying the hardware. Thus digital hardware and associated software provide a greater degree of flexibility in system design. Also, there is often a higher order of precision achievable with digital hardware and software compared with analog circuits and analog signal processing systems.

For all these reasons, there has been an explosive growth in digital signal processing theory and applications over the past three decades. DSP is a key enabling technology for many applications in fields such as telecommunications, consumer electronics, hearing aid devices, disk drives, and navigation. DSP functions can be implemented using a range of implementation approaches: Application Specific Integrated Circuit (ASIC), Fixed Point ASIC (FASIC), general-purpose processors, and programmable digital signal processors are all commonly used.

In this connection, a digital hearing aid uses variety of advanced DSP algorithms such as noise reduction or echo cancellation. For this customized DSP processors or generic DSP cores can be used. Products available in the market today are all based on customized DSP cores as power dissipation is an important issue in it. Although, analog signal processors are available, it is not generally used, as we discuss here.

#### 1.3.1 Advantages of Digital over Analog Signal Processing

Digital signal processing techniques have numerous advantages. Digital circuits are not dependent on precise values of digital signals for their operation. Digital circuits are less sensitive to changes in component values. They are also less sensitive to variations in temperature, ageing and other external parameters. Digital processing of a signal facilitates the sharing of a single processor among a number of signals by time-sharing. This reduces the processing cost. In addition multirate processing is possible only in digital domain. Storage of digital data is very easy. Digital process-

ing is much more suited for processing very low frequency signals [3-4].

#### 1.3.2 Basic Elements of a Digital Signal Processing Systems

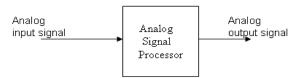

Most of the signals encountered in science and engineering are analog in nature. That is, the signals are functions of a continuous variable, such as time or space, and usually take on values in a continuous range. Such signals may be processed directly by appropriate analog systems (such as filters or frequency analyzers or frequency multipliers) for the purpose of changing their characteristics or extracting some desired information. In such a case we say that the signal has been processed directly in its analog form, as shown in figure 1.1.

Figure 1. 1: Analog signal processing

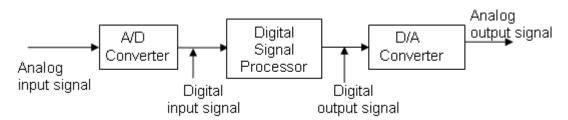

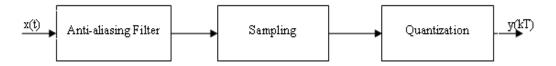

Both the input signal and the output signal are in analog form. Digital signal processing provides an alternative method for processing the analog signal as shown in figure 1.2. To perform the processing digitally, there is a need for an interface between the analog signal from outside world and the digital processor. This interface is called an analog to digital converter. The output of the A/D converter is a digital signal that is appropriate as an input to the digital processor [3-4].

Figure 1. 2: Block diagram of a digital signal processing system.

The digital signal processor may be a large programmable digital computer or a small microprocessor programmed to perform the desired operations on the input signal. It may also be a hardwired digital processor configured to perform a specified set of operations on the input signal. Programmable machines provide the flexibility to change the signal processing operations through a change in the software, whereas hardwired machines are difficult to reconfigure.

Since in this dissertation various DSP algorithms would be handled, it is important to have a clear understanding of the DSP processor.

#### 1.4 DSP Processor

A DSP processor is designed to support fast execution of the repetitive, numerically intensive computations characteristic of digital signal processing algorithms. The most often cited of these features is the ability to perform a multiply-accumulate operation (often called a "MAC") in a single instruction cycle. A single-cycle MAC operation is extremely useful in algorithms that involve computing a vector dot-product, such as digital filters. Such algorithms are very common in DSP applications. To achieve a single-cycle MAC, all DSP processors include a multiplier and accumulator as central elements of their data-paths [3-4].

A second feature shared by DSP processors is the ability to complete several accesses to memory in a single instruction cycle. This allows the processor to fetch an instruction while simultaneously fetching operands for the instruction, and/or storing the result of the previous instruction to memory. Typically, multiple memory accesses in a single cycle are possible only under restricted circumstances.

To allow numeric processing to proceed quickly, DSP processors incorporate one or more dedicated address generation units. The address generation units operate in parallel with the execution of arithmetic instructions, forming the addresses required for data memory accesses. The address generation units typically support addressing modes tailored to DSP applications.

Because many DSP algorithms involve performing repetitive computations, most DSPs provide hardware support for efficient looping. Often, a special loop or repeat instruction is provided which allows the programmer to implement for next loop without expanding any instruction cycles for updating and testing the loop counter and branching to the top of the loop. Finally, to allow low-cost, high-performance input and output, many DSPs incorporate one more serial or parallel I/O interfaces, and specialized I/O handling mechanisms such as low- overhead interrupts or DMA.

### 1.4.1 Fixed Versus Floating Point number

DSP chip word size determines resolution and dynamic range. In the fixed point processors, a linear relationship exists between word size and dynamic range. The fixed

point DSPs have either 16 or 24 bit data bus. There are four common ways to represent  $2^{16} = 65,536$  possible bit patterns for a number. In unsigned integer, the stored number can take on any integer value from 0 to 65,535. Similarly, signed integer uses two's complement to make the range include negative numbers, from -32,768 to 32,767. With unsigned fraction notation, the 65,536 levels are spread uniformly between 0 and 1. Lastly, the signed fraction format allows negative numbers, equally spaced between -1 and 1.

The floating point chip performs integer or real arithmetic. Normally, floating point DSP formats are 32 data bits wide and in which 24 bits form the mantissa and 8 bits make up the exponent. This results in many more bit patterns than for fixed point,  $2^{32} = 4,294,967,296$  to be exact. A key feature of floating point notation is that the represented numbers are not uniformly spaced. All floating point DSPs can also handle fixed point numbers, a necessity to implement counters, loops, and signals coming from the ADC and going to the DAC. However, this doesn't mean that fixed point math will be carried out as quickly as the floating point operations; it depends on the internal architecture.

Fixed point arithmetic is much faster than floating point in general purpose computers. However, with DSPs the speed is about the same, a result of the hardware being highly optimized for math operations. The internal architecture of a floating point DSP is more complicated than for a fixed point device. All the registers and data buses must be 32 bits wide instead of only 16; the multiplier and ALU must be able to quickly perform floating point arithmetic, the instruction set must be larger (so that they can handle both floating and fixed point numbers), and so on. Floating point (32 bit) has better precision and a higher dynamic range than fixed point (16 bit). In addition, floating point programs often have a shorter development cycle, since the programmer doesn't generally need to worry about issues such as overflow, underflow, and round-off error. On the other hand, fixed point DSPs have traditionally been cheaper than floating point devices.

### 1.4.2 Architecture of Digital Signal Processor

Although fundamentally related, DSP processors are significantly different from general purpose processors (GPPs). To understand why, we need to know what is involved in signal processing. Some of the most common functions performed in the digital domain are signal filtering, convolution and fast Fourier transform. In mathe-

matical terms, these functions perform a series of dot products. This brings us to the most popular operation in DSP: the multiply and accumulate (MAC).

The first major architectural modification that distinguished DSP processors from the early GPPs was the addition of specialized hardware that enabled single-cycle multiplication. DSP architects also added accumulator registers to hold the summation of several multiplication products. Accumulator registers are typically wider than other registers, often providing extra bits, called guard bits, to avoid overflow. Typical DSP algorithms require more memory bandwidth than the Von Neumann architecture used in GPPs. Thus, most DSP processors use some forms of Harvard architecture which has two separate memory spaces, typically partitioned as program and data memories.

Although, this may seem that DSP applications must pay careful attention to numeric accuracy - which is much easier to do with a floating-point data path, fixed-point machines tend to be cheaper (and faster) than comparable floating-point machines. To maintain accuracy without the complexity of a floating-point data path, DSP processors usually include a good support for saturation arithmetic, rounding, and shifting.

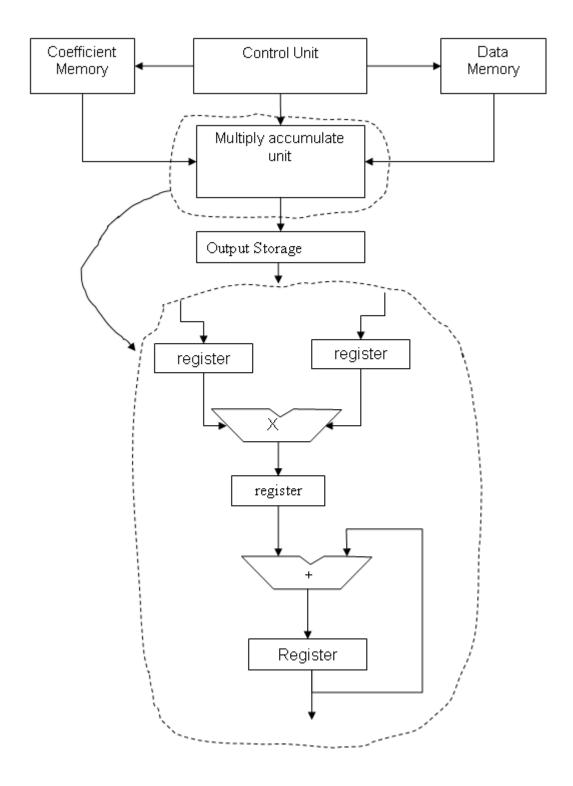

Another distinction of DSP processors is specialized addressing modes that are useful for common signal-processing operations and algorithms. The generic architecture of a DSP processor is shown in figure 1.3. The architecture has two separate memory spaces (program and data) which can be accessed simultaneously. This is similar to the Harvard architecture employed in most of the programmable DSPs. The arithmetic unit performs fixed point computation on numbers represented in "2's" complement form. It consists of a dedicated hardware multiplier and an adder/subtractor connected to the accumulator so as to be able to efficiently execute the multiply-accumulate (MAC) operation.

In our dissertation we will use different digital filters for hearing aid application; we discuss that in the next section.

Figure 1. 3: Generic DSP processor architecture

#### 1.5 Digital Filters

#### 1.5.1 Analog and Digital filters

In signal processing, the function of a filter is to remove unwanted parts of the signal, such as random noise, or to extract useful parts of the signal, such as the components lying within a certain frequency range. The following block diagram in figure 1.4 illustrates the basic idea.

Figure 1. 4: Basic idea of a filter

There are two main kinds of filter, analog and digital. They are quite different in their physical makeup and in how they work. An analog filter uses analog electronic circuits made up from components such as resistors, capacitors and op-amps to produce the required filtering effect. Such filter circuits are widely used in such applications as noise reduction, video signal enhancement, graphic equalizers in hi-fi systems, and many other areas. There are well-established standard techniques for designing an analog filter circuit for a given requirement. At all stages, the signal being filtered is an electrical voltage or current which is the direct analogue of the physical quantity (e.g. a sound or video signal or transducer output) involved.

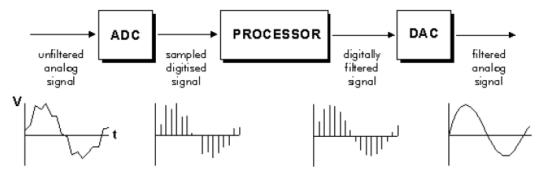

A digital filter uses a digital processor to perform numerical calculations on sampled values of the signal. The processor may be a general-purpose computer such as a PC, or a specialized DSP (Digital Signal Processor) chip. The analog input signal must first be sampled and digitized using an ADC (analog to digital converter). The resulting binary numbers, representing successive sampled values of the input signal, are transferred to the processor, which carries out numerical calculations on them. These calculations typically involve multiplying the input values by constants and adding the products together. If necessary, the results of these calculations, which now represent sampled values of the filtered signal, are output through a DAC (digital to analog converter) to convert the signal back to analog form. In a digital filter, the signal is represented by a sequence of numbers, rather than a voltage or current. The figure 1.5 shows the basic setup of such a system.

Figure 1. 5: Basic set-up of a digital filter

#### 1.5.2 Advantages of digital filters

The following list gives some of the main advantages of digital filters over analog counterpart [3].

- A digital filter is programmable, i.e. its operation is determined by a program stored in the processor's memory. This means the digital filter can easily be changed without affecting the circuitry (hardware). An analog filter can only be changed by redesigning the filter circuit.

- Digital filters are easily designed, tested and implemented on a generalpurpose computer or workstation.

- The characteristics of analog filter circuits (particularly those containing active components) are subject to *drift* and are dependent on temperature.

Digital filters do not suffer from these problems, and so are extremely *stable* with respect both to time and temperature.

- Unlike their analog counterparts, digital filters can handle *low frequency* signals accurately. As the speed of DSP technology continues to increase, digital filters are being applied to high frequency signals in the RF (radio frequency) domain, which in the past was the exclusive preserve of analog technology.

- Digital filters are very much more *versatile* in their ability to process signals in a variety of ways; this includes the ability of some types of digital filter to adapt to changes in the characteristics of the signal.

- Fast DSP processors can handle complex combinations of filters in parallel or cascade (series), making the hardware requirements relatively *simple* and *compact* in comparison with the equivalent analog circuitry.

#### 1.6 Algorithms for Hearing Aid Design

Most of the hearing devices use modern signal processing techniques in order to reduce noise or feedback signal that results from the secondary path i.e the sound signal that propagates from the speaker to the microphone. This causes undesired howling effects. From this point of view we have carried out a series of literature review on signal processing used in hearing aid devices.

#### 1.6.1 Feedback cancellation in hearing aids

Feedback cancellation can be performed in various ways like

- a. constrained and unconstrained adaption

- b. open loop and closed loop identification

- c. bias and unbiased feedback cancellation

In constrained adaption, when applying constraint on the magnitude of the adaptive weight vectors, it greatly reduces the probability that adaptive filter will cancel the narrowband input signals [5]. This paper indicates that constrained adaption has better efficiency than the unconstrained adaption.

Feedback cancellation that employs two types of open loop identifications is being reported in the literature [6]. The first algorithm uses second order signal statistics to adapt the weights while the second algorithm uses higher order statistics to adapt the weights. According to the theory; higher order statistics should be able to perform better to eliminate white noise and pink noise, but it has been shown that the higher order statics fails when the SNR of input signal falls below 0 dB [6]. Finally it has been concluded that in this case second order statistics performs better than higher order statistics in speech enhancement of hearing aid devices.

Acoustic feedback in hearing aid devices reduces the maximum usable gain. In continuous adaption of feedback cancellation, a bias is found in the adaptive filter's estimate in feedback estimation. It has been reported that using a delay in the forward or cancellation path of the hearing aid device, bias can be reduced by 15 dB [7].

Use of fixed length FIR filters in feedback path with linear gain in hearing aids has been reported and can avoid instability and howling effect in everyday use [8]. Undesired effect of the acoustic feedback in hearing aids can be reduced with an internal feedback path which gives a limiting estimate of the external feedback path.

In paper [9] LMS or RLS algorithm is used and it has been shown that limiting estimate will be biased if there exists an error in the model. To mitigate this problem, a second signal is added to the output of the hearing aid to avoid the non linearity of the hearing aid. Frequency domain adaptive filtering is used for this analysis.

Psychoacoustic Approach has been applied to hearing aid problems and in this method use of a post-filter used in the forward path has been reported [10]. This paper also reports that psycho-acoustically motivated weighting rule method of adaption is good for getting natural near end speech and results in less annoying residual noise.

Some authors use non-uniform digital FIR filter bank [11] for hearing aid application. This filter is designed by taking eight non-uniform spaced subbands that uses frequency response masking technique to give a stopband attenuation of 80 dB. It is reported that, non-uniform digital filter banks achieve good matching between audiograms and magnitude response of the filter banks with a low computational cost.

Multi delay line filter applications are reported [12] in which smaller transforms are used and ensures better control over stability obtained. Feedback cancellation in hearing aids based on Filtered-X LMS has also been reported [13]. The identification is thus done in closed loop. In this case optimal estimate is biased when the identification is performed in closed loop and the input signal to the hearing aid is not white. The bias could be avoided if the spectrum of the input signal was known and the data used to update the internal feedback is pre-filtered. The effects of different choices of the design variables of the Filtered-X LMS are taken into account and the optimal estimate of the Filtered-X LMS with an individually adjusted fixed filter showed the best agreement with the desired estimate.

Previous discussion of feedback cancellation uses single channel for feedback cancellation. When a stereophonic echo cancellation is used, there exists non-unique solution [14]. The non-uniqueness problem exists due to coherence between the two incoming audio channels. One proven solution to this problem is to distort the signals with a nonlinear device. This presents a novel theory that gives an insight to the existing links between: i) Coherence and level of distortion, and ii) coherence and achievable misalignment of the stereophonic echo canceller. Furthermore, when an adaptive nonlinear device is used for adaption, a pre-specified maximum misalignment is maintained while improving the perceived quality by minimizing the introduced distortion [14].

Howling is very annoying problem to the hearing-aid users that limits the maximum usable gain of hearing-aid devices. The paper [15], presents an effective feedback cancellation system where a time-varying all-pass filter together with a delay in the forward path is used for de-correlating the input and output signals of the hearing aid plant. The adaptive filter in the hearing aid performs continuous adaptation based on the input signal. The output signal of the hearing aid is processed by a 2nd-order APF whose frequency is varied using a low-frequency modulator. It has been reported that the time varying all pass filter can significantly reduce the weight-vector misalignment with a small delay in the forward path.

Most of the above discussion uses narrowband signals for feedback cancellation, wideband adaptive feedback cancellation techniques do not provide satisfactory performance for reducing feedback oscillation in hearing aids. A band-limited adaptive feedback cancellation algorithm using normalized filtered-X LMS technique provides good cancellation efficiency, convergence behaviour and better output sound quality [16] for speech signals than other wideband method of feedback cancellation.

A generalized noise reduction scheme has been proposed, called the Spatially Pre processed, Speech Distortion Weighted, Multichannel Wiener Filter (SP-SDW-MWF) [17]. It uses Generalized Sidelobe Canceller (GSC) and a multichannel Wiener filtering technique as extreme cases. Compared with the widely studied GSC with Quadratic Inequality Constraint (QIC-GSC), the SP-SDW-MWF achieves a better noise reduction performance for a given maximum speech distortion level. In this paper, a low-cost, stochastic gradient implementation of the SP-SDW-MWF is implemented using frequency domain approach for better speed up convergence and reduces computational complexity. Experimental results with a behind-the-ear hearing aid show that the proposed frequency-domain stochastic gradient algorithm preserves the benefit of the exact SP-SDW-MWF over the QIC-GSC.

For hearing aid users the direct method of adaptive feedback cancellation is widely used to mitigate feedback; however it is less effective for high forward path gains due to the inherent bias in the feedback path estimate. This bias can be reduced at the expense of artificial delays which can potentially introduce pre-echo and "comb filter" effects. The direct method also tends to cancel tonal audio signals such as alarms and music. This study [18] uses closed-loop system identification for unbiased feedback cancellation which does not possess the negative characteristics manifested by the direct method, but uses an identification signal. It uses two-stage method which

employs two adaptive filters, one to identify the entire closed-loop, and another to extract the feedback path response was the preferred unbiased method due to its low computation and good feedback identification particularly during "howling." This paper presents that unbiased feedback cancellation method is better than the widely used direct method.

Stereophonic acoustic echo cancellation has gained much interest in recent years due to the non-uniqueness and misalignment problems that are caused by the strong inter-channel signal coherence. A novel adaptive filtering approach is used to reduce inter-channel coherence which is based on a selective-tap updating procedure [19]. This tap-selection technique is then applied to the normalized least-mean-square, affine projection and recursive least squares algorithms for stereophonic acoustic echo cancellation. This technique reports convergence rate is significantly upon the existing techniques.

An adjustable filter-bank based algorithm has been tested and developed for hearing aid systems [20]. The implementation of this filter-bank algorithm on co-chlear-prosthesis' DSP-board enables to generate and control electrical stimulating pulses. In conventional hearing aids driven by DSP, filter bank-based algorithm permits an ease adjustment of speech amplification, which is fully programmable within the considered sounds' spectrum. In each device, a programmable spectrum cut-up permits to adjust filters' bands relatively to patient's pathology. Programming via host computer enables flexibility in speech amplification for conventional hearing aids, and in cochlea's stimulation for cochlear prostheses. It combines handiness, ease of use and safety features to help meet individual's diverse needs. A computer illustration, based on spectrum cutting-up, was designed to identify filters' outputs. Hence, with this visual measure, clinicians could set up experiments for adjusting correctly hearing aid's operation-parameters.

We have already brought out the importance of digital filters, DSP and their importance in Digital hearing aid applications. Furthermore, it is also important that the hearing aid must consume low power and be designed with lowest possible area. The details of low power VLSI design and the approaches adopted in this dissertation will be discussed in the next chapter. Our purpose is to design low power digital filter for hearing aid, we have only chosen suitable algorithms, demonstrated their performance through FPGA implementation.

#### 1.7 Objective of the thesis

From the study of FPGA/ CMOS based techniques of hearing aid; various types of methodologies [11-17] have been applied to hearing aid devices. Some of the circuit level implementation shows the use of direction microphone has been proposed where as others uses switched MOSFET technology to achieve low power. In architectural level of design; use of filtering cores, number presentation like 2's complement and Sign magnitude presentation have been proposed.

In spite of the best efforts, there is still a lot of scope to find and optimize the algorithms suited for hearing aid. However, the algorithm should be hardware implementable as ultimately an IC need to be designed. While designing it is also important to focus on two major issues

- a. Low power design

- b. Small area.

Keeping in view of above considerations we define the following objectives of the thesis.

- a. To investigate and find out suitable algorithm(s) for Hearing aid application with a hardware implementation perspective.

- b. To find out an adaptive algorithm that is simple to implement in hard-ware and also should be less power consuming. Adaptive algorithms are likely to perform better in terms of spectral sharpening and noise reduction. Moreover, since we are attempting for low power design, low power techniques would be adopted at algorithmic abstraction level.

- c. Usually some component(s) appear repeatedly in VLSI design. If we can reduce power consumption of such a component at circuit level and incorporate the same in the design; the total power reduction would improve. Therefore, we would proceed to investigate at the circuit level to find a low power circuit that would be extensively used in filter design.

- d. To combine circuit level and algorithm level low power consumption in a filter for hearing aid application and to make a real-time validation.

- e. To implement for all the filter structures in FPGA.

f. To develop an experimental setup and validate the simulation results and the concepts through experiment for the best structure evaluated in the thesis.

#### 1.8 Organization of thesis

**Chapter-I** presents introduction to the hearing aid design and basics of literature survey based on algorithms applied to hearing aids.

**Chapter-II** presents a detailed literature survey low power methodology and FPGA/Circuit level design of digital filters for hearing aids application. Some of the multiplier structures has been studied and simulated.

**Chapter-III** introduces the use of a Decimation filter for hearing aid application using 'Distributed arithmetic' when the incoming signal is sampled at a higher than Nyquist rate. The filter is being designed using Matlab Simulink and Xilinx System generator. The filter is being tested and the power estimation is carried out.

**Chapter-IV** introduces the use adaptive filter that incorporates adaptive lattice filter. The filter is being designed using Booth-Wallace multiplier and is implemented in Virtex-II pro board from Xilinx. In this implementation both area and power are computed. Furthermore power computation is also done for the entire hearing aid architecture.

**Chapter-V** A novel method has been adopted for FIR filter implementation. This filter is being designed and implemented using a MAC unit and FDF (Folded Direct Form) structure for FIR filter. A suitable clocking strategy is adopted which reduces glitches that facilitates reduction of power dissipation. A novel dual edge triggered technique latch together with clock gating strategy is being used to achieve low power and it is observed that this FIR filter in conjunction with clock gating and low power latch consumes low power compared to other designs.

**Chapter-VI** covers comparison between different types filter and the filter with low power consumption is being implemented with real time signals using Xilinx Virtex-II pro board and spectral analysis is done for three different signals such as speech,

music and voice and music both. The filter successfully works for all these signals. The gain for the filter is being calculated and is found to be between 9 dB to 27 dB which matches specifications given by most of the hearing aid manufacturers.

In **Chapter-VII**, conclusions are brought out and some further research scopes are suggested.

## Chapter - II

## Low Power VLSI Techniques for Digital Filters for Hearing aid applications

#### 2.1 Review of Low Power Methods used in Filters

The objective of this dissertation is to come up with digital filters that are suitable for hearing aid applications. Here we need to design filters that would provide necessary amplification and frequency response. Furthermore, it is also important that the evolved structures must be hardware realizable and reusable [21], so that we can develop a product. Low power is an essential constraint for hearing aids, therfore suitable low power strategy need to be applied. Low power VLSI techniques at different abstraction levels are applied while designing filter.

Various types of methodologies are employed for low power design. These are

- 1. Algorithmic level

- 2. Structural level and

- 3. Circuit level.

Various filter applications designed at circuit level and FPGA based digital filters also have been studied. Using circuit level design methodologies, an adaptive directional microphone for hearing aid application for DSP VLSI application has been designed with area of 0.67mm<sup>2</sup> based on 250 nm technology with power consumption about 45uW achieved at 1.25V supply [22]. Use of switched MOSFET(SM) technique for low power filter design and a SM programmable band-pass filter for hearing aid application is reported [23]. A high efficiency and low distortion switching power amplifier is proposed and is designed for micropower low-voltage hearing aids. The experimental results show that the proposed circuit has 0.27% total harmonic distortion and 90% power efficiency while the dc output bias current is 19 mA at 1.5V supply voltage which is used in circuit level design for achieving low power [24].

An ultra-low-power delayed least mean square (DLMS) adaptive filter operating in the sub-threshold region for hearing aid applications is reported in which sub-threshold operation was accomplished by using a parallel architecture with pseudo nMOS logic style. The parallel architecture enables to operate the system at a lower clock rate and reduced supply voltage while maintaining the same throughput. Pseudo nMOS logic operating in the sub-threshold region (subpseudo nMOS) provided better power-delay product than sub-threshold CMOS (sub-CMOS) logic [25]. Simulation results show that the DLMS adaptive filter can operate at 22 kHz using a 400-mV supply voltage to achieve 91% improvement in power compared to a nonparallel, CMOS implementation. The result is validated by designing testing of the an carry

save array multiplier test chip with of size a 0.35 m, 23.1 kHz, 21.4 nW, where an adaptive body biasing scheme is used for compensating process, supply and temperature variations.

The following paragraph describes various algorithmic and structural levels to accomplish low power objectives. A multiplier free architecture using Distributed Arithmetic (DA) is used in the implementation of LMS adaptive filter and high speed LMS adaptive filter can be designed using DA in FPGA [26]. Also algorithmic filter cores (structures) for filter implementation has been investigated in order to minimize the switched capacitance of the multipliers and data/coefficient buses [27] and it is reported that a power saving upto 39% can be achieved.

Multipliers play an important role design of filters. A novel design technique for deriving highly efficient multipliers that operate on a limited range of multiplier [28] values is presented in the literature. Using the technique, Xilinx Virtex field programmable gate array (FPGA) implementations for a discrete cosine transform and poly-phase filter were derived with area reductions of 31%–70% and speed increases of 5%–35% when compared to designs using general-purpose multipliers. This design gives better result than other fixed coefficient methods.

Reconfigurable hardware devices make it possible to change structure of digital electronic circuits at runtime. Using reconfigurable devices as a platform for Evolvable hardware (EHW) is well suited for real-time adaptive systems [29] which present both the filter as well as the evolution parameters for adaptive filter implementation on a single Field programmable gate array (FPGA). This paper uses context based switching to obtain a smaller hardware and fast adaption.

Low power block based filtering cores has been studied and specially used for low power filter implementation [30]. This uses algorithmic flow for low power filter design and also uses 2's complement and SM (sign magnitude) number presentation. It has been reported that as compared to convention filtering cores, a power reduction of 49% and area overhead of 5% is increased.

A clock based Low power and area efficient FIR filter of 32 tap using two 16 tap macros implementation has been implemented. Using different conditions for a coded coefficient and data, and a power saving of 35% and 44% improvement as compared to radix-4 modified booth algorithm is being reported [31]. Designs of programmable finite impulse response (FIR) digital filters have demonstrated that the use of broadcast input data and control can lead to a high performance-to-cost ratio. Effect

of the interconnect delay to the cycle time and its negative effects on both scalability and cost-effectiveness of such broadcast designs have been presented in the literature [32]. Further it is shown; speed and density improvements secured through technology scaling can be maintained by a fully pipelined design in which both data and control signals are restricted to local connections [33]. In this design filter coefficients are loaded in bit-parallel form with no increase in the number of input pins, thereby facilitating and speeding up run-time adaptation to the application environment. Another feature of variable-precision coefficients is that, it can be accommodated easily and flexibly, with no speed penalty. This type of design methods can be applied for the design of application- specific and embedded parallel architectures.

There is a continuous drive for methodologies and approaches of low power design. The design of low power systems for different portable applications is not a simple task [33]. This is because of the number of constraints that influence the power consumption of a device. In addition to issues of performance and functionality, there is a need to satisfy strict test coverage constraints. In the same work [33] a brief study on the impact of DSP architectural realization, multiplier type, and the choice of number representation on the overall power consumption of DSP devices have been carried out. Furthermore the effect of DFT circuits on the overall performance has been studied. A hearing aid device is considered as an example of a system with strict power/area constraints. It is being shown that the choice of multiplier architecture and number representation should be carefully considered when specific DSP architectural choices are made.

The design and implementation of decimation filter used for hearing aid applications is reported in [33]. The implementation of the decimation filters using the canonical signed digit (CSD) representation is being carried out [34]. Each digital filter structure is simulated using Matlab, and its complete architecture is captured using DSP blockset and Simulink. The filter has been implemented on Xilinx FPGA using Virtex-II technology. The resulting architecture is hardware efficient and consumes less power compared to conventional decimation filters [34]. Compared to the comb-FIR-FIR architecture, the designed decimation filter architecture contributes to a hardware saving of 69%; in addition, it reduces the power dissipation by 83%, respectively. In another work a very fast and low complexity FIR filter implemented using CSD multiplication is realized using shifters, adders and subtractors [35]. In this method, the critical path is minimized using pipeline registers equal to propagation

delay of an adder. For 100% speed up an area overhead of 5% increase has been reported.

Another work describes a scheme for the implementation of low power cores for hearing aid applications [36]. In this work, power saving schemes has been investigated using two approaches. First method uses macro-component framework which allows the rapid assembly of the cores on easy-to-verify hierarchical plug-in basis and second one uses system-on-chip strategy [36]. The cores are embedded within an ARM-based system-on-chip platform for design and testing of FIR filters. Using this method, it is shown that effective power manipulation is possible by power management strategies.

The design and implementation of an improved hardware-based evolutionary digital filter (EDF) version 2 is being reported in [37]. EDF is an adaptive digital filter which is controlled by adaptive algorithm based on evolutionary computation. The hardware based EDF version 1 consists of two sub-modules, that is, a filtering and fitness calculation (FFC) module and a reproduction and selection (RS) module. The FFC module has high computational ability to calculate the output and the fitness value since its sub-modules run in parallel. However, hardware size of the FFC module is large, and many machine cycles are needed. Thus, in the hardware-based EDF version 2 combines two modules to reduce its hardware size and machine cycles [36]. A synthesis result on the FPGA shows that the clock frequency is 65.5MHz and the maximum sampling rate of the hardware-based EDF version 2 is 4,948.1Hz. Moreover, the hardware-based EDF version 2 is 15.7 times faster than the hardware-based EDF version 1.

A coefficient segmentation algorithm for low power FIR filter implementation has been proposed and the algorithm decomposes individual coefficients into two primitive sub-components [38]. The decomposition, performed using a heuristic approach, divides a given coefficient such that a part is produced which can be implemented using a single shift operation leaving another part with a reduced word length to be applied to the coefficient input of the hardware multiplier. This results in a significant reduction in the amount of switched capacitance and consequently power consumption. The algorithm has been used with a number of practical FIR filter examples achieving up to 63% saving in power.

Another paper describes the design of a compact, ultra low power continuous time programmable filter suitable for feedback cancellation filters in hearing aids and open loop identification is being performed [39]. Because of the complexity of the transfer function the number of poles in the cancellation filter is fairly large, ultra-low power transconductance cell with large linear range has been designed. The power consumption for a transconductance cell is comparable to the theoretical minimum bound and is measured to be 0.8μW at a 3V supply has been reported. The linear input range for this cell is 2Vp-p. The complete filter has been designed, implemented and fabricated in a 2μ CMOS technology.

In spite of all the cited work [21-39] there is still a lot of scope for alternate designs at different abstraction levels on low power perspective. Therefore an attempt is being made to design digital filters that are not only functionally suitable, but those would operate at low power that is one of the primary constraints for hearing aid design.

In order to proceed further, we now discuss the basics of low power VLSI design. This study would provide us greater insight for low power VLSI design of digital filters.

## 2.2 Basics of Low power VLSI Design

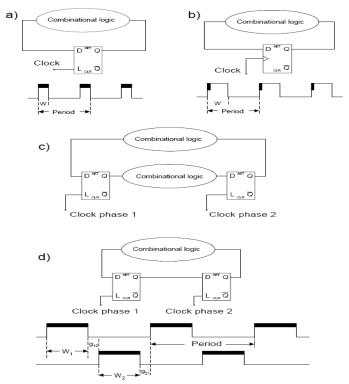

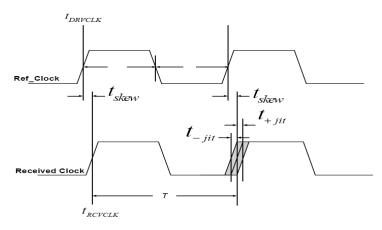

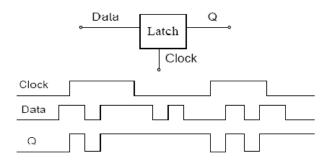

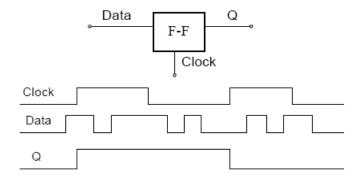

In the past few years there has been an explosive growth in the demand for portable computing and communication devices, from mobile telephones to sophisticated multimedia systems [40]. This interest in these devices has enhanced the requirement of developing low-power signal processors and algorithms, as well as the development of low-power general purpose processors. Designers have been able to reduce the energy requirements of particular functions, such as video compression, by several orders of magnitude [41]. This reduction has come as a result of focusing on the power dissipation at all levels of the design process, from algorithm design to the detailed implementation, however, there has been little work done to understand how to design energy efficient processors.