## DESIGN OF RANDOM NUMBER GENERATOR AND ITS DELAY AND POWER OPTIMIZATION

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

**Bachelor of Technology**

in

**Electronics and Communication Engineering**

Ву

SUNIL KUMAR BEHERA 10407007

And

10407009

**Department of Electronics and Communication Engineering**

**National Institute of Technology**

Rourkela

2008

## National Institute of Technology Rourkela

### **CERTIFICATE**

This is to certify that the thesis entitled, DESIGN OF RANDOM NUMBER GENERATOR AND ITS DELAY AND POWER OPTIMIZATION" submitted by Sri Sunil Kumar Behera and Sri Vivek Sharma in partial fulfillments for the requirements for the award of Bachelor of Technology Degree in Electronics and Communication Engineering at National Institute of Technology, Rourkela (Deemed University) is an authentic work carried out by them under my supervision and guidance.

To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other University / Institute for the award of any Degree or Diploma.

Date: Prof. Dr. K.K Mahapatra

Dept. of Electronics and Communication Engineering

National Institute of Technology

Rourkela - 769008

**ACKNOWLEDGEMENT**

I would like to articulate my profound gratitude and indebtedness to my project guide

Prof.Dr. K.K Mahapatra who has always been a constant motivation and guiding factor

throughout the project time in and out as well. It has been a great pleasure for me to get an

opportunity to work under him and complete the project successfully.

An undertaking of this nature could never have been attempted with our reference to and

inspiration from the works of others whose details are mentioned in references section. I

acknowledge my indebtedness to all of them. Last but not the least, my sincere thanks to all of

my friends who have patiently extended all sorts of help for accomplishing this undertaking.

Sunil Kumar Behera

Vivek Sharma

3

## **CONTENTS**

| ABSTRACT                                              | 05   |

|-------------------------------------------------------|------|

| CHAPTER 1: Introduction                               | .06  |

| CHAPTER 2: Transient simulation and power measurement | 08   |

| CHAPTER 3: Random number generators                   | 17   |

| CHAPTER 4: Project Simulation                         | 21   |

| CHAPTER 5: Results and conclusion                     | 27   |

| REFERENCES                                            | . 31 |

### **ABSTRACT:**

A digital system is tested and diagnosed during its lifetime on numerous occasions. Test and diagnosis must be quick and have very high fault coverage. One way to ensure this is to specify test as one of the system functions, so it becomes self test. The system has several PCBs, each of which, in turn has multiple chips. The system controller can activate self-test simultaneously on all PCBs. These test result help to isolate faulty chips and boards. In this project Linear Feedback Shift Register (LFSR) method has been used to generate pseudo random tests. This method uses very little hardware and is currently the preferred built in self test pattern generation method. Mentor Graphics Design architect tool was used for designing of circuit. It was also used for measuring power and delay associated with the circuit for different technologies.

| INTRODUCTION |  |

|--------------|--|

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

#### **INTRODUCTION**

A digital system is tested and diagnosed during its lifetime on numerous occasions. Test and diagnosis must be quick and have very high fault coverage. One way to ensure this is to specify test as one of the system functions, so it becomes self test. At the highest level of systems test, the testing function is frequently implemented in software. Many digital systems designed at AT&T circa 1987 had self-test, usually implemented in software. Its most common use was in maintenance and repair diagnostics. Although this approach provided flexibility, it also had disadvantages. The fault coverage and the diagnostic resolution of those software implemented tests were not as high as desired. The diagnostic resolution may be poor because the software must test parts that are difficult to test, and therefore it may not effectively determine which part is at fault. Also, software tests can be long, slow and expensive to develop. It is also most effective to consider testing as early in the design cycle as possible. These lead to schedule slippages for product introduction.

| TRANSIENT SIMULATION AND MEASUREMENTS |  |  |

|---------------------------------------|--|--|

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

|                                       |  |  |

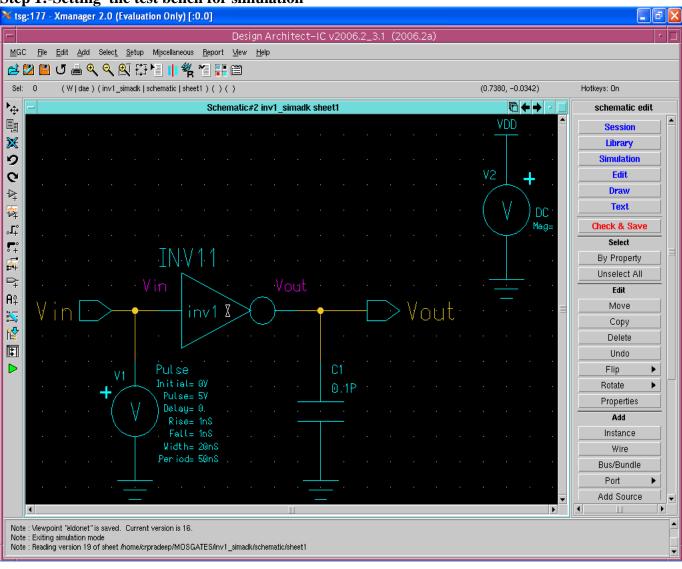

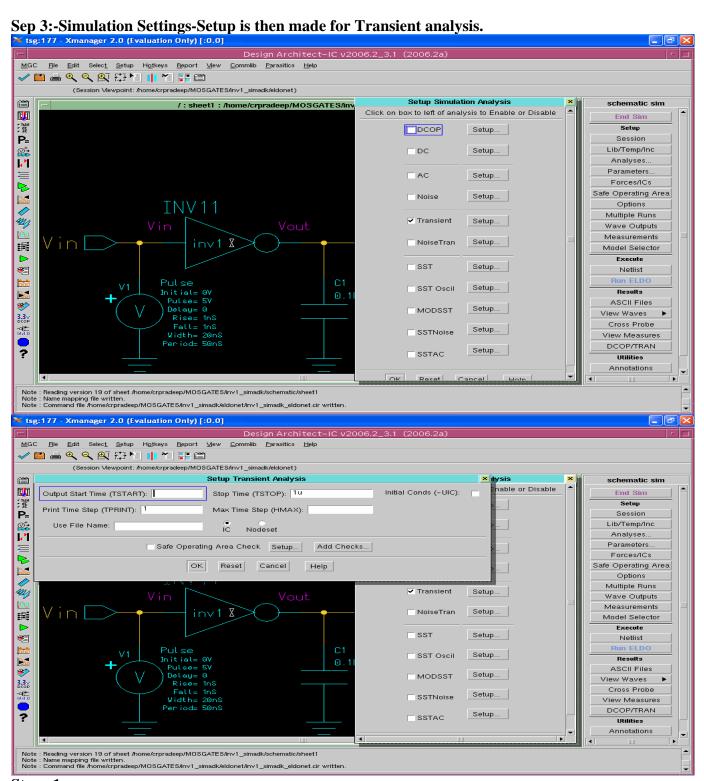

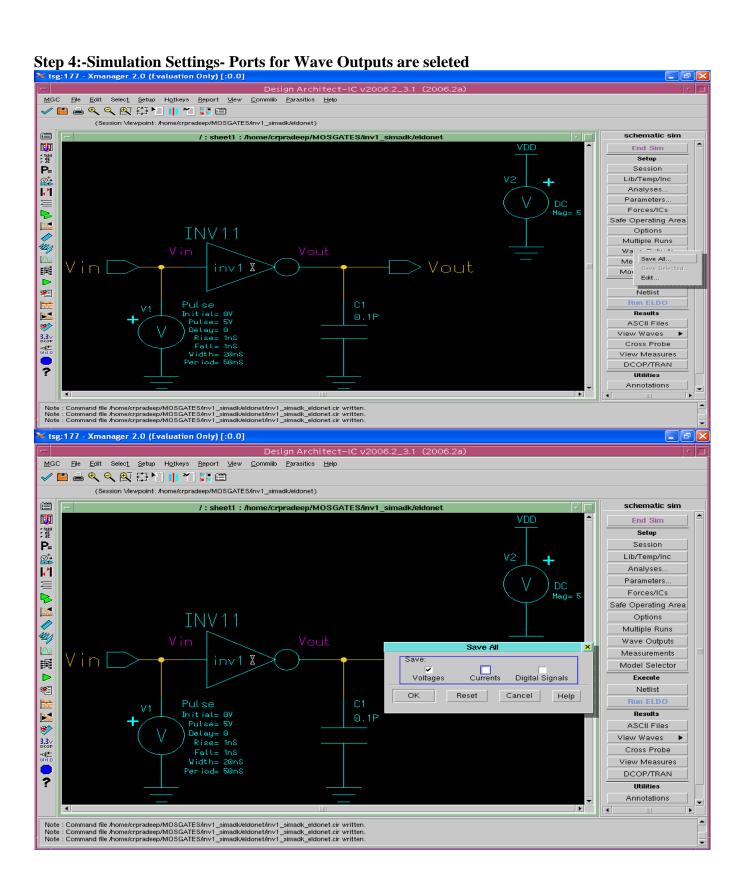

### TRANSIENT SIMULATION AND MEASUREMENTS

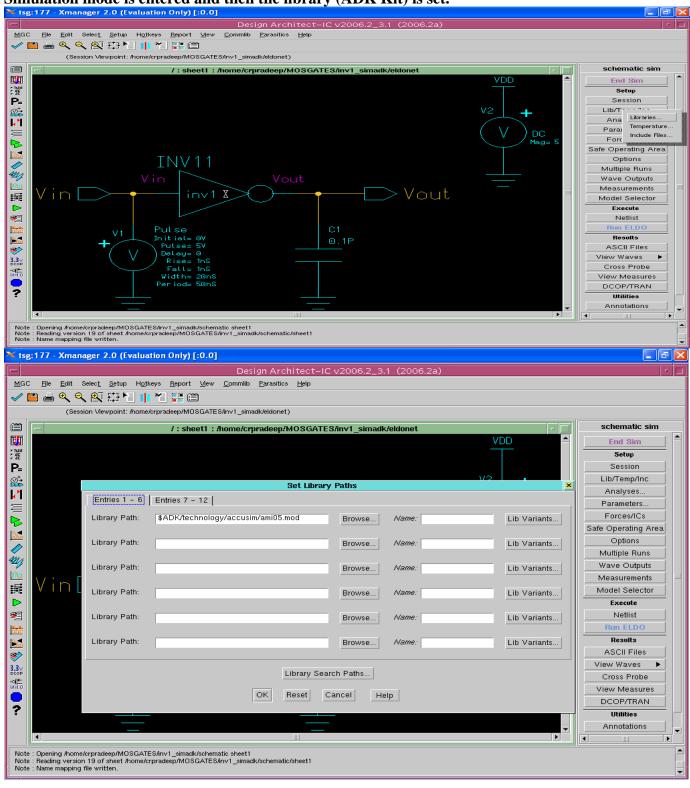

Step 2:- Simulation Settings – Library Settings Simulation mode is entered and then the library (ADK Kit) is set.

Stop:-1 u

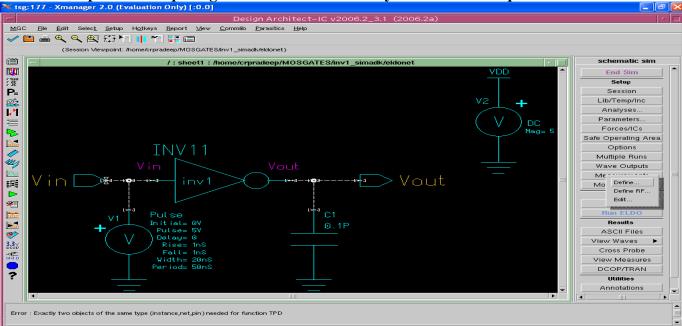

### **MEASUREMENT OF PROPAGATION DELAY(TPD)**

Here both Input and Output signals are selected. Ctrl key is used for multiple selection

#### **Select Menu->TPD**

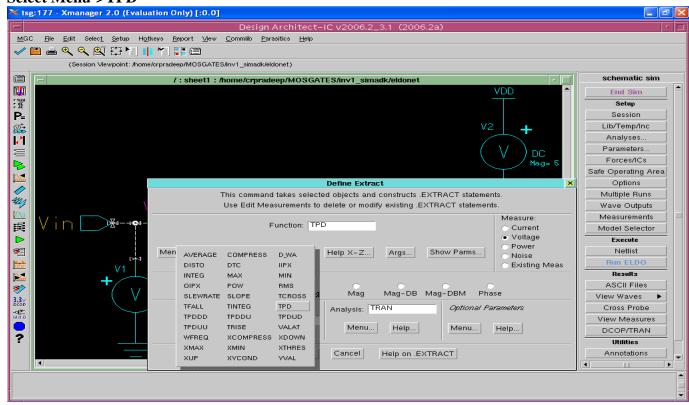

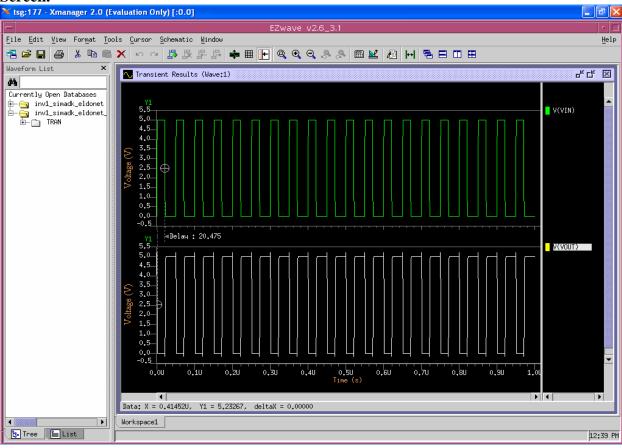

**Vout\_Delay** is written in the label ->OK tsg:177 - Xmanager 2.0 (Evaluation Only) [:0.0]  $\underline{\mathsf{M}}\mathsf{GC} \quad \underline{\mathsf{File}} \quad \underline{\mathsf{E}}\mathsf{dit} \quad \mathsf{Selec}\underline{\mathsf{t}} \quad \underline{\mathsf{S}}\mathsf{etup} \quad \mathsf{H}\underline{\mathsf{o}}\mathsf{tkeys} \quad \underline{\mathsf{R}}\mathsf{eport} \quad \underline{\mathsf{V}}\mathsf{iew} \quad \underline{\mathsf{C}}\mathsf{ommlib} \quad \underline{\mathsf{P}}\mathsf{arasitics} \quad \underline{\mathsf{H}}\mathsf{elp}$ (Session Viewpoint: /home/crpradeep/MOSGATES/inv1\_simadk/eldonet) schematic sim  ${\it I: sheet1: /home/crpradeep/MOSGATES/inv1\_simadk/eldonet}$ End Sim r Tran Setup P= Session Lib/Temp/Inc 2 Ñ Analyses.. Parameters.. 澶 Forces/ICs Mag= 5 Safe Operating Area Options 44/ This command takes selected objects and constructs .EXTRACT statements. Multiple Runs Use Edit Measurements to delete or modify existing .EXTRACT statements. Wave Outputs Measurements Measure: 熏 Function: TPD Current Model Selector Voltage Power **≆**≣ Netlist Help A-S... Help T-W... Help X-Z... Noise nin Ma Run ELDO Existing Meas Format: Results ASCII Files **\*** Default Mag-DB Mag-DBM Phase View Waves 3.3v Analysis: TRAN Optional Parameters Cross Probe -o|± ⊌=1.0 Label: Vout\_Delay View Measures Menu... Help... Menu... Help... DCOP/TRAN Utilities ОК Reset Cancel Help on .EXTRACT Annotations

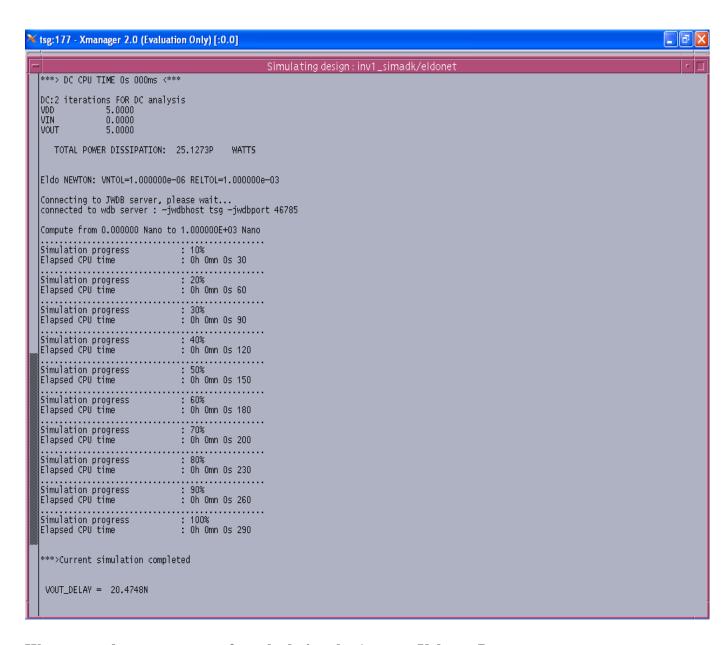

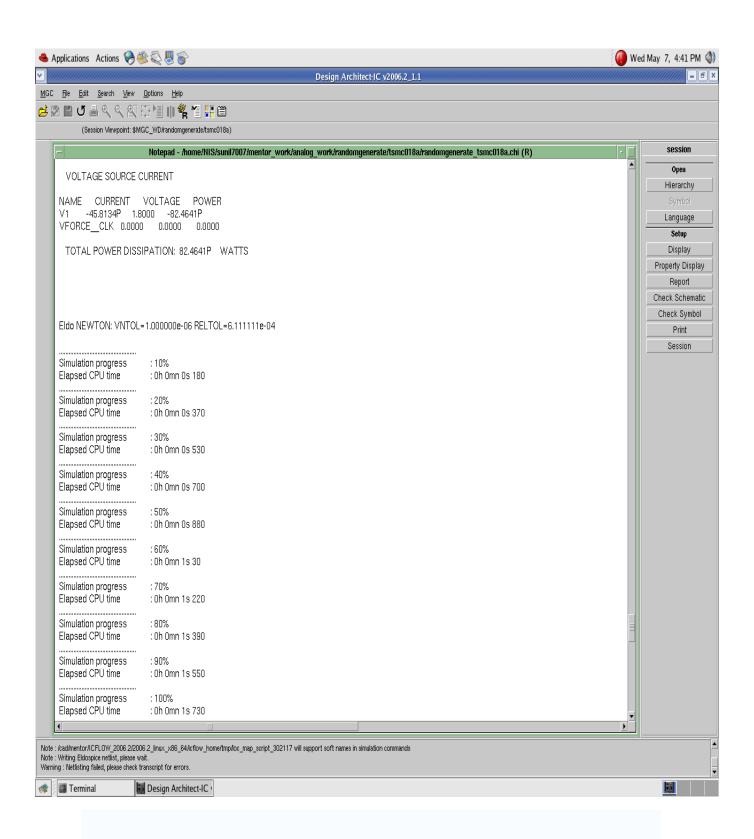

Run ELDO ->In the transcript we can see the Total Power Dissipation and also the Vout\_Delay

We can use the measurement for calculating the Average Voltage, Power etc.

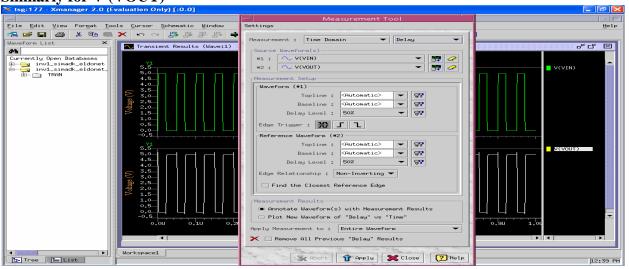

We can also measure the delay in the wave form viewer using "Measurement Tool" Click on the V (VIN) and click on the waveform database in the Measurement tool. Similarly for V (VOUT)

Click on Apply and then close the Measurement tool in order to get the Below Screen.

RANDOM NUMBER GENERATORS

#### RANDOM NUMBER GENERATOR

A digital system is tested and diagnosed during its lifetime on numerous occasions. Test and diagnosis must be quick and have very high fault coverage. One way to ensure this is to specify test as one of the system functions, so it becomes self test. At the highest level of systems test, the testing function is frequently implemented in software. Many digital systems designed at AT&T circa 1987 had self-test, usually implemented in software. Its most common use was in maintenance and repair diagnostics. Although this approach provided flexibility, it also had disadvantages. The fault coverage and the diagnostic resolution of those software implemented tests were not as high as desired, the diagnostic resolution may be poor because the software must test parts that are difficult to test, and therefore it may not effectively determine which part is at fault. Also, software tests can be long, slow and expensive to develop. It is also most effective to consider testing as early in the design cycle as possible. These lead to schedule slippages for product introduction

.The benefit of BIST is lower test development cost, because BIST can be automatically added to a circuit with a CAD tool. Also, BIST generally provides a 90 to 95% fault coverage, and even 99% in exceptional cases. The test engineer need no longer worry about back driving problem of in-circuit test, or how much memory is available in the ATE.BIST always requires added circuit hardware for a test controller to operate the testing process, design for testability hardware in the circuit to improve fault coverage during BIST, a hardware pattern generator to generate test-patterns algorithmically during testing, and some form of hardware response compactor to compact the circuit

response during testing. The relative costs of added logic gates are declining, because hardware continue to become cheaper, but the relative costs of added long wires for test mode control are not really decreasing. Also, the test hardware can consume extra power, which is an additional cost. Since the BIST circuitry uses chip area, a final BIST cost is a decrease in the chip yield and chip reliability, due to the increased area. BIST feasibility for a system must be evaluated using benefit-cost analysis, in the context of assessing total life cycle costs.

For design and test development, BIST significantly reduces the costs of automatic test-pattern generalizes (ATPG), also reduces the likelihood of disastrous product introduction delays because fully- designed system cannot be tested. Such a delay has occurred in the Intel Merced project due to unexpected delays in inserting testability hardware into the chip, and fabrication line problems. There is a slight cost increase due to BIST in design and test development, because of the added time required to design and adds pattern generators, response compacters, and testability hardware. However, our experience is that this is less costly than test development with ATPC.

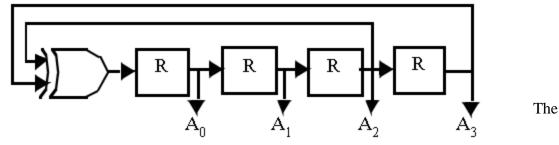

## The block diagram of the generator is

Pseudo-Random number generator.

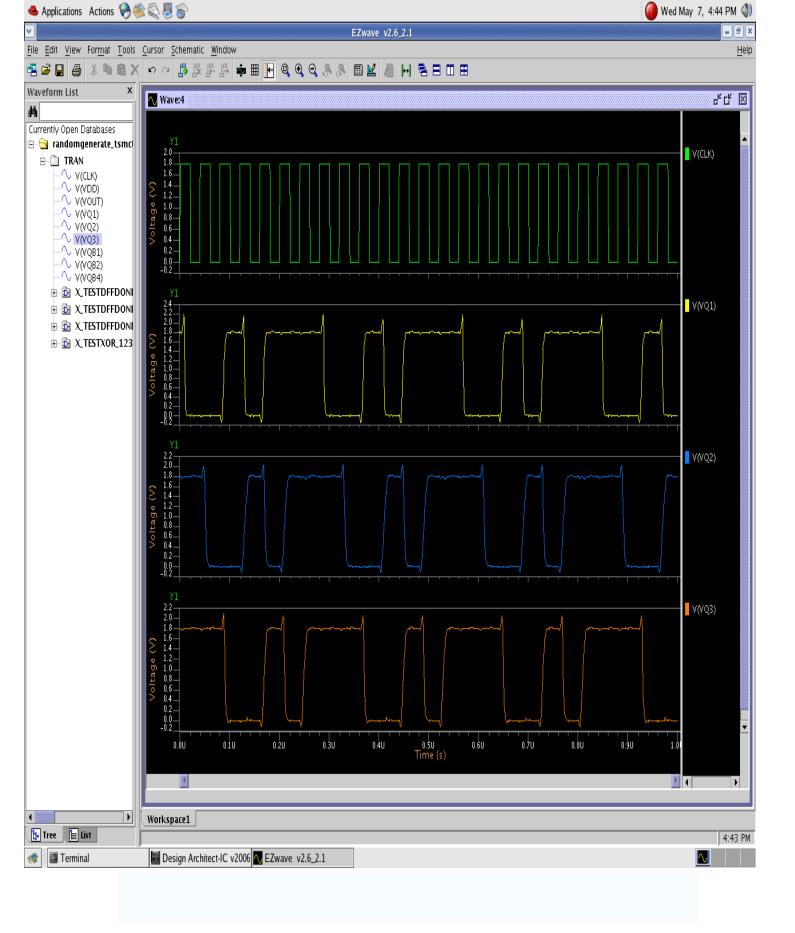

random number generator used in the project uses linear feedback shift register (LFSR) to generate pseudo random tests. This method uses very little hardware and is currently the preferred BIST pattern generation method. The circuit designed uses positive edge triggered D-Flip Flops as registers and a XOR Gate for implementing random number generation.

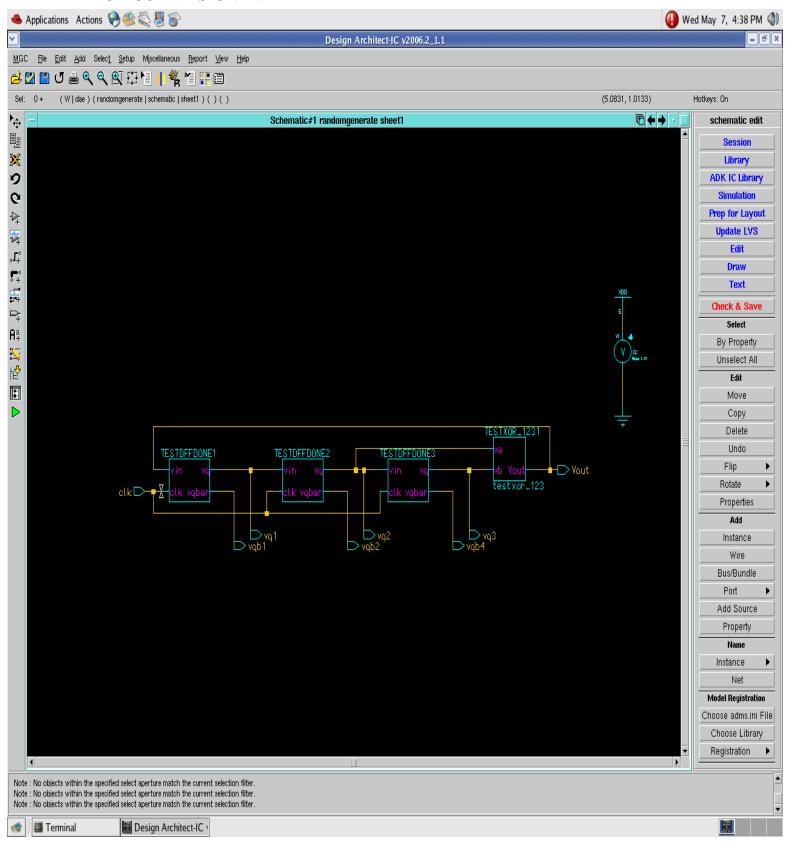

PROJECT SIMULATION

#### CIRCUIT DESIGNED.

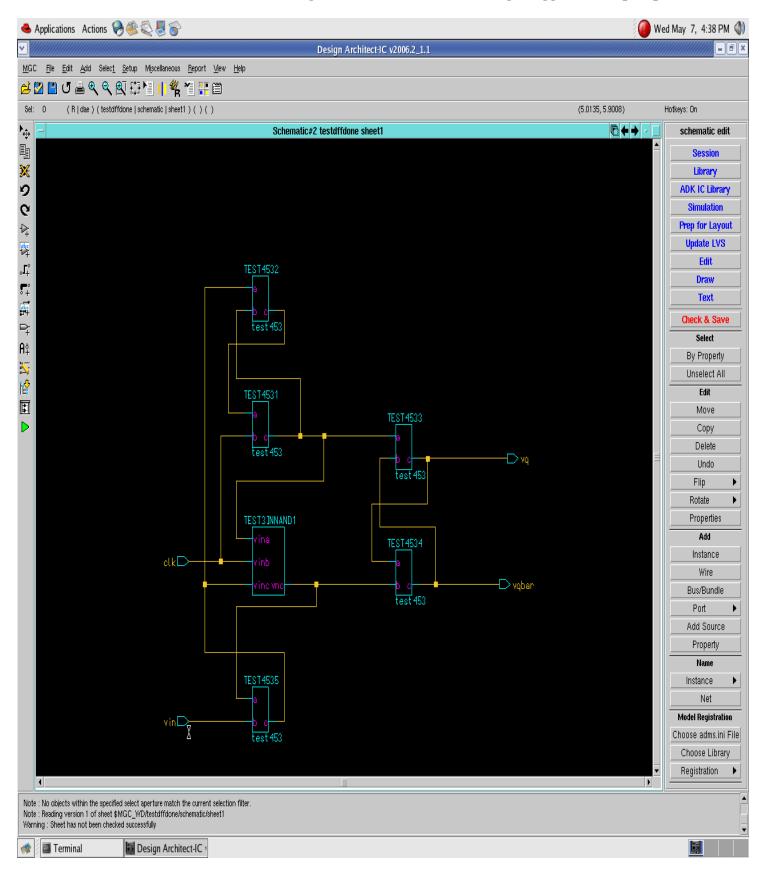

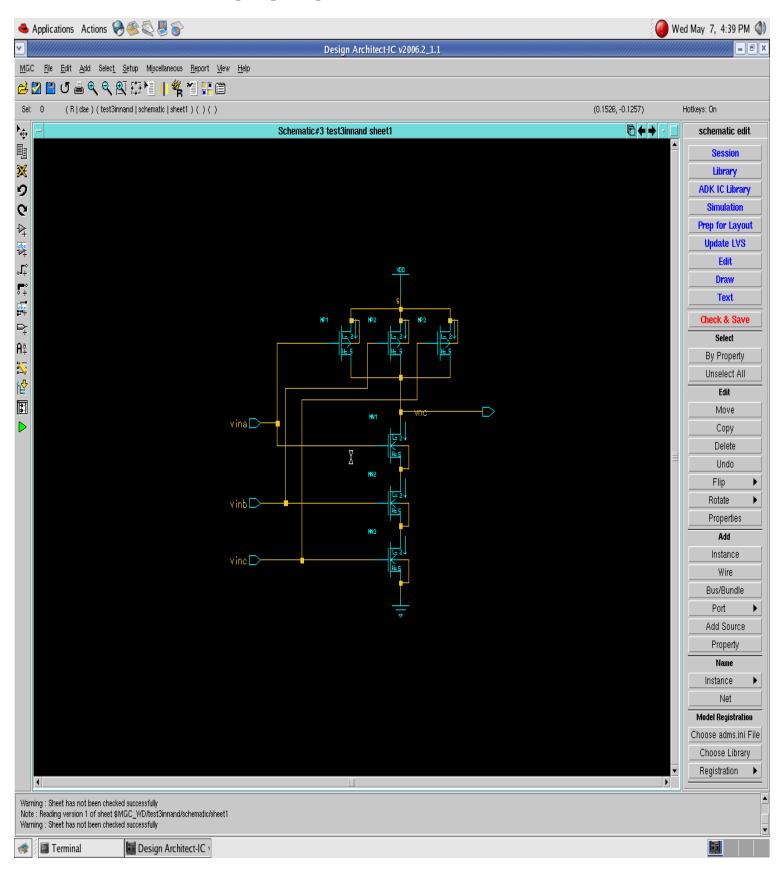

Sub-Circuit of random number generator circuit: Positive edge triggered D-flip flop

Sub-Circuit of D-Flip Flop: 3-input NAND Gate.

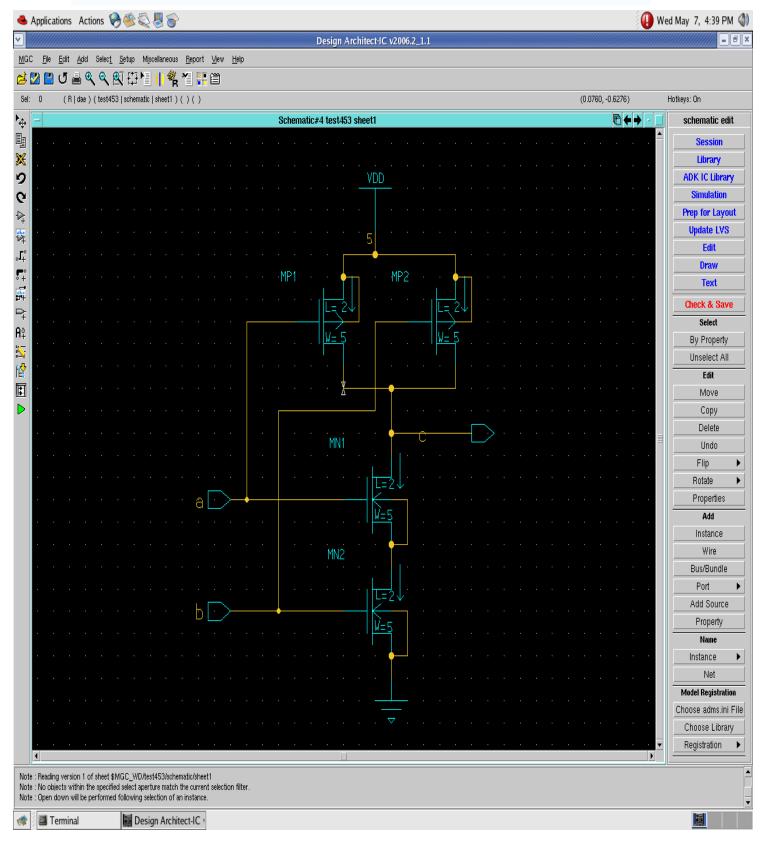

## **Sub-Circuit of D-Flip Flop: 2-input NAND Gate**

Power dissipation results of the circuit.

**RESULTS AND CONCLUSION**

**RESULTS**

By applying the various technology the result obtained were as follows

| TECHNOLOGY | POWER        | DELAY    |

|------------|--------------|----------|

| AMI05      | 82.46pwatts  | 16.459ns |

| AMI12      | 83.00pwatts  | 10.688ns |

| TSMC035    | 86.59pwatts  | 12.36ns  |

| TSMC025    | 375.54pwatts | 14.78ns  |

| TSMC018    | 588.96pwatts | 14.43ns  |

|            |              |          |

### **CONCLUSION**

From the results the various power and delay values for random number generator circuit was obtained. In ami technology class ami12 the delay was 10.688ns which is less as compared to ami05. Hence the former one was better for the designing the circuit. In tsmc technology class tsmc035 had the least power taken and the smallest propagation delay hence most suitable for the circuit designed. The tsmc018 technology has the least size hence can be preferred where the area of the hardware needed is small.

### **REFRENCES**

### Websites referred:

- 1. www.wikipedia.com

- 2. <u>www.howstuffswork.com</u>

- 3. www.swarthmore.edu.com

### Books referred:

1. Digital Integrated Circuits by Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic.